# Digitale Integrierte Schaltungen 384.086

# Beispielsammlung mit Lösungen

Peter Rössler Herbert Nachtnebel Rosemarie Velik Christian Stoif Martin Pongratz

# **ICT**

E384 Institut für Computertechnik

Technische Universität Wien

WS 2012/2013

# Inhaltsverzeichnis

# Angabenteil

| 1. M  | oore-Automaten                                                | 3  |

|-------|---------------------------------------------------------------|----|

| 1.1.  | Phasenschieber                                                | 5  |

| 1.2.  | Schaltknoten                                                  | 6  |

| 1.3.  | Gray-Code Zähler                                              | 7  |

| 1.4.  | Arbiter                                                       | 8  |

| 2. M  | ealy-Automaten                                                | 9  |

| 2.1.  | Zweistelliger Binärzähler mit Übertragsausgang                | 9  |

| 2.2.  | Up/Down Counter                                               | 10 |

| 2.3.  | Vereinfachung von Zustandsgraphen                             | 10 |

| 2.4.  | Ready-Logik                                                   | 11 |

| 2.5.  | HDB3-Encoder                                                  | 12 |

| 3. Pr | ogrammschaltwerke                                             | 14 |

| 3.1.  | Programmschaltwerk für Drehstromsignal                        | 14 |

| 3.2.  | Anzeigeeinheit für seriell übertragene Daten                  | 15 |

| 3.3.  | Programmschaltwerk zur Drehrichtungsbestimmung                | 16 |

| 3.4.  | Programmschaltwerk mit Addierer                               | 18 |

| 3.5.  | Multiplizierer                                                | 19 |

| 4. H  | ardwarebeschreibungssprachen                                  | 21 |

| 4.1.  | Beschreibung von Multiplexern in VHDL                         | 21 |

| 4.2.  | Beschreibung von Flip-Flops und Registern in VHDL             | 21 |

| 4.3.  | Beschreibung von Addierern, Subtrahierern und Zählern in VHDL | 23 |

| 4.4.  | Beschreibung von Decodern in VHDL                             | 24 |

| 4.5.  | Beschreibung von Moore- und Mealy-Automaten in VHDL           | 24 |

| 4.6.  | Aufbau von hierarchischen Designs mittels VHDL                | 25 |

| 5. Si | mulation, Testen und Design Rules                             | 26 |

| 5.1.  | Design for Testability                                        | 26 |

| 5.2.  | Simulation in VHDL                                            | 26 |

| 5.3.  | Scan-Path-Design                                              | 27 |

## Lösungsteil

| 1. M  | oore-Automaten                                                | 28 |

|-------|---------------------------------------------------------------|----|

| 1.1   | Phasenschieber                                                | 28 |

| 1.2.  | Schaltknoten                                                  | 30 |

| 1.3.  | Gray-Code Zähler                                              | 33 |

| 1.4.  | Arbiter                                                       | 35 |

| 2. M  | lealy-Automaten                                               | 38 |

| 2.1.  | Zweistelliger Binärzähler mit Übertragsausgang                | 38 |

| 2.2.  | Up/Down Counter                                               | 41 |

| 2.3.  | Vereinfachung von Zustandsgraphen                             | 47 |

| 2.4.  | Ready-Logik                                                   | 50 |

| 2.5.  | HDB3-Encoder                                                  | 52 |

| 3. Pi | rogrammschaltwerke                                            | 55 |

| 3.1   | Programmschaltwerk für Drehstromsignal                        | 55 |

| 3.2.  | Anzeigeeinheit für seriell übertragene Daten                  | 57 |

| 3.3.  | Programmschaltwerk zur Drehrichtungsbestimmung                | 60 |

| 3.4.  | Programmschaltwerk mit Addierer                               | 62 |

| 3.5.  | Multiplizierer                                                | 63 |

| 4. H  | ardwarebeschreibungssprachen                                  | 66 |

| 4.1.  | Beschreibung von Multiplexern in VHDL                         | 66 |

| 4.2.  | Beschreibung von Flip-Flops und Registern in VHDL             | 69 |

| 4.3.  | Beschreibung von Addierern, Subtrahierern und Zählern in VHDL | 74 |

| 4.4.  | Beschreibung von Decodern in VHDL                             | 79 |

| 4.5.  | Beschreibung von Moore- und Mealy-Automaten in VHDL           | 81 |

| 4.6.  | Aufbau von hierarchischen Designs mittels VHDL                | 87 |

| 5. Si | mulation, Testen, Design Rules                                | 90 |

| 5.1.  | Design for Testability                                        | 90 |

| 5.2.  | Simulation in VHDL                                            | 95 |

| 5.3.  | Scan-Path-Design                                              | 99 |

### 1. Moore-Automaten

#### 1.1. Phasenschieber

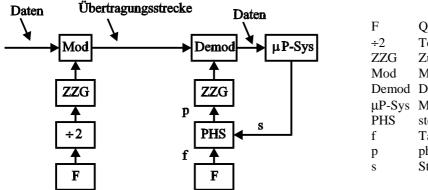

Für die Übertragung von Daten über stark gestörte Kanäle, wie zum Beispiel das 230V-Netz, ist die Spread-Spectrum-Technik mit Direct Sequence besonders gut geeignet. Der serielle Datenstrom wird dabei mit einer periodischen, binären Zufallszahlenfolge<sup>1</sup> moduliert, sodaß sich die Energie des Signals auf eine große Bandbreite verteilt. Der Empfang erfolgt durch eine zweite codesynchrone Modulation mit derselben Zufallszahlenfolge, die den Originalzustand der Daten wiederherstellt.

F Quarz-Taktgenerator

÷2 Teiler durch zwei

ZZG Zufallszahlengenerator

Mod Modulator

Mod Modulator

Demod Demodulator

μP-Sys MikroprozessorsystemPHS steuerbarer Phasenschieberf Taktsignal vom Quarzoszillator

p phasenkorrigierter Takt

Steuersignal für Phasenschieber

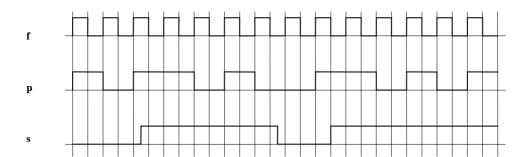

Um die Synchronität der Zufallszahlenfolge im Empfänger einstellen zu können, benötigt man einen Phasenschieber PHS, der den quarzgenauen Takt f kontrolliert verzögert. Die Steuerung der Taktverzögerung erfolgt vom Mikroprozessorsystem über s. Ändert sich der Pegel an s nicht, so ist die Frequenz von p gleich f/2. Bei einer (asynchronen) Änderung des Pegels an s wird eine Halbwelle von p von 1/f auf 2/f verlängert. Ändert sich der Pegel an s während der nächsten Halbwelle von p erneut, so wird die Halbwelle von p um weitere 1/f verlängert. Es findet erst wieder ein Flankenwechsel an p statt, wenn sich der Zustand von s während einer Halbwelle 1/f von p nicht ändert. Die lokale periodische Zufallszahlenfolge läßt sich mit PHS über s solange verschieben, bis sie mit dem Eingangssignal codesynchron ist.

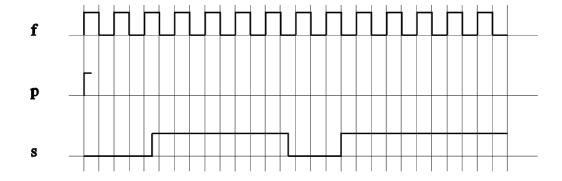

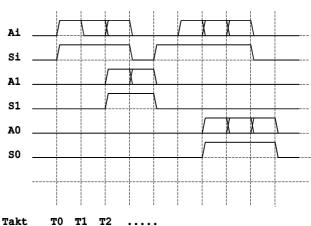

#### a) Ergänzen Sie im nachstehenden Zeitdiagramm das Signal p.

<sup>&</sup>lt;sup>1</sup> Der gebräuchliche Ausdruck *periodische Zufallszahlenfolge* führt oft zu Mißverständnissen. Unter einer periodischen Zufallszahlenfolge versteht man eine Abfolge von Zahlen, welche sich periodisch wiederholt. Da die Abfolge sich periodisch wiederholt ist sie voraussagbar und damit nicht wirklich zufällig. Da die Folge jedoch nicht monoton ist, erscheint die Reihenfolge der Zahlen bei entsprechend großer Periode völlig zufällig. Daraus ergibt sich die Bezeichnung *periodische Zufallszahlenfolge*. Derartige Folgen werden in der Praxis mit rückgekoppelten Schieberegistern erzeugt.

- b) Wie groß ist die Frequenz p in Abhängigkeit von f und s? Geben Sie den sinnvollen Wertebereich von s und den daraus folgenden Wertebereich für p an.

- c) Nehmen Sie für das Propagation Delay aller verwendeten Bauteile den theoretischen Wert von 0 an. Muß der Automat mit positiv oder negativ flankengetriggerten Flip-Flops realisiert werden?

- d) Warum wird für die Realisierung der Aufgabenstellung ein Moore-Automat und kein Mealy-Automat verwendet?

- e) Wie viele Zustände besitzt der Automat?

- f) Wie kann man erreichen, daß die Ausgangsgleichung für p möglichst einfach ist (siehe Fußnote <sup>2</sup>)?

- g) Entwerfen Sie den Zustandsgraphen und beschriften Sie die Übergangsvektoren mit den zugehörigen Eingangs-/Ausgangsgrößen. Geben Sie die Bedeutung der einzelnen Zustände an.

- h) Ermitteln Sie die Zustandsübergangstabelle und die zugehörigen Ausgangswerte für p aus dem Zustandsgraphen unter Berücksichtigung von Punkt f).

- i) Geben Sie die Gleichungen für die Realisierung mit D-Flip-Flops an.

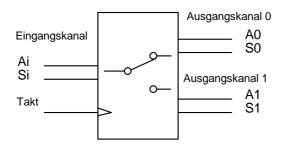

#### 1.2. Schaltknoten

Für eine Datenpaketvermittlungsanlage ist ein Schaltknoten zu entwerfen. Der Schaltknoten besitzt einen Eingangskanal und zwei Ausgangskanäle zur Vermittlung serieller synchroner Datenpakete. Zusätzlich steht der datensynchrone Takt T zur Verfügung. Der Eingangskanal wird entsprechend dem ersten Bit jedes Datenpakets (Adreßbit) an einen der beiden Ausgangskanäle durchgeschalten (Adreßbit=0  $\Rightarrow$  Ausgangskanal 0, Adreßbit=1  $\Rightarrow$  Ausgangskanal 1). Im Bild ist die Übertragung von zwei Paketen dargestellt, wobei das erste Paket an den Ausgangskanal 1 und das zweite Paket an den Ausgangskanal 0 weitergeschaltet wird. An den Ausgangskanälen werden die Daten ohne dem Adreßbit ausgegeben. Die ausgegebenen Pakete sind damit immer um ein Bit kürzer als die empfangenen Pakete.

Alle drei Kanäle bestehen jeweils aus einer A-Leitung und einer S-Leitung. Auf den A-Leitungen werden die Daten seriell übertragen. Die S-Leitungen sind während der Datenübertragung high und

© Herbert Nachtnebel, TU-Wien

<sup>&</sup>lt;sup>2</sup> Anmerkung: Der Einfachheit halber wird der Index n bei Signalen und Variablen oft weggelassen. Es entspricht hier also beispielsweise der Ausgang p gleich p<sup>n</sup>.

im Ruhezustand low. Beachten Sie, daß auch die Signalleitungen Sn am Ausgang erst bei Ausgabe des um das Adreßbit verkürzten Datenpaketes den Pegel 1 annehmen. Die Größe der Pakete am Eingang (exklusive dem Adreßbit) liegt zwischen einem Bit und beliebig vielen Bits. Durch eine oder mehrere Nullen auf S werden die Datenpakete voneinander getrennt. Ist S auf 0, so sind die Daten auf A ungültig.

Um eine beliebige Kaskadierbarkeit der Knoten zu gewährleisten, sollen die Knoten als Moore-Automaten ausgeführt werden. Bei Mealy-Automaten würde jeder Knoten mindestens eine Gatterlaufzeit Verzögerung der Datenleitung gegenüber der Taktleitung verursachen, was bei einer Hintereinanderschaltung mehrerer Knoten zu ungewollten Laufzeiteffekten führt. Für die Realisierung sollen D-Flip-Flops verwendet werden.

- a) Zeichnen Sie den Zustandsgraphen für den Schaltknoten. Beschriften Sie die Kanten des Graphen mit  $A_iS_i$  und die Zustände mit den zugehörigen Ausgangssignalen in der Form  $A_0S_0A_1S_1$ .

- b) Durch Fehler bei der Übertragung werden Pakete generiert die nur mehr ein Bit lang sind. Das Paket besteht also nur mehr aus dem Adreßbit. Erweitern Sie den Zustandsgraphen derart, daß solche Pakete vom Schaltknoten einfach ignoriert, d.h. nicht weitergeleitet werden. Alle folgenden Punkte dieses Beispiels beziehen sich auf diesen erweiterten Zustandsgraphen.

- c) Wie viele Flip-Flops sind für die Realisierung des Automaten notwendig?

- d) Wählen Sie eine Codierung für die Zustände und geben Sie die vollständige Zustandsübergangstabelle an. Wie wählen Sie die Folgezustände und Ausgangssignale in nicht benötigten Zuständen? Diskutieren Sie die verschiedenen Möglichkeiten.

- e) Geben Sie die Gleichungen für A<sub>0</sub>, S<sub>0</sub> und D<sub>1</sub> an.

- f) Mithilfe der Schaltknoten soll eine Vermittlungsanlage für einen Sender und 6 Empfänger aufgebaut werden. Wie viele Schaltknoten werden zum Aufbau der Vermittlungsanlage benötigt? Welche Länge haben die einzelnen Pakete, wenn mit jedem Paket 8 Datenbits übertragen werden sollen?

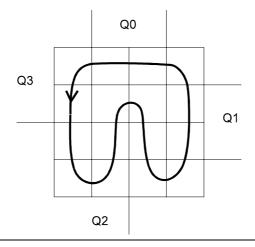

# 1.3. Gray-Code Zähler

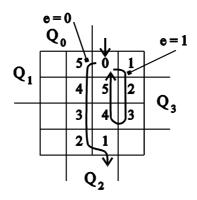

Es ist ein Gray-Code Zähler zu entwerfen, der mit Hilfe von 4 JK-Flip-Flops alle möglichen 16 Zustände entsprechend folgendem KV-Diagramm durchläuft:

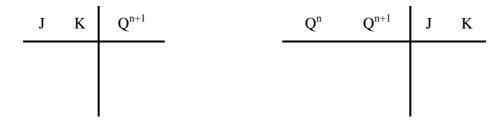

- a) Geben Sie die charakteristische Gleichung für das JK-FF an.

- b) Ergänzen Sie die beiden folgenden Tabellen für das JK-FF.

- c) Zeichnen Sie ein KV-Diagramm mit den vier Variablen Q<sub>3</sub><sup>n</sup>, Q<sub>2</sub><sup>n</sup>, Q<sub>1</sub><sup>n</sup>, Q<sub>0</sub><sup>n</sup>. Tragen Sie in die untere Hälfte jedes der 16 Felder des KV-Diagramms ein, welchen Zuständen Q<sub>3</sub><sup>n</sup>, Q<sub>2</sub><sup>n</sup>, Q<sub>1</sub><sup>n</sup>, Q<sub>0</sub><sup>n</sup> das entsprechende Feld entspricht.

- a) Tragen Sie in die obere Hälfte jedes der 16 Felder des KV-Diagramms aus c) die Folgezustände  $Q_3^{n+1}$ ,  $Q_2^{n+1}$ ,  $Q_1^{n+1}$ ,  $Q_0^{n+1}$  ein.

- b) Geben Sie die 8 KV-Diagramme für die Größen  $J_3^n$ ,  $J_2^n$ ,  $J_1^n$ ,  $J_0^n$  und  $K_3^n$ ,  $K_2^n$ ,  $K_1^n$ ,  $K_0^n$  an.

- f) Bestimmen Sie mittels der KV-Diagramme aus e) die Gleichungen für alle J und K.

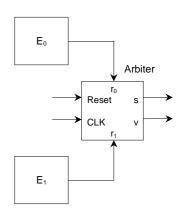

#### 1.4. Arbiter

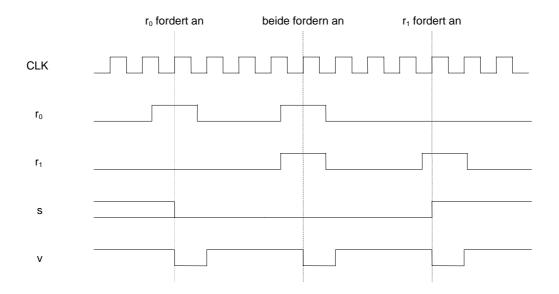

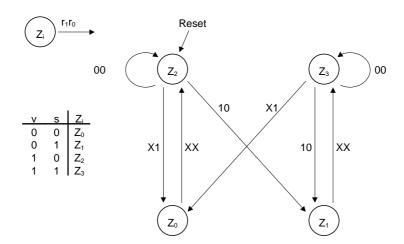

Es ist ein Arbiter (Arbitrierungsautomat) zu entwerfen. Er besitzt die Eingangssignale  $r_0$  und  $r_1$  (request), Reset und CLK sowie die Ausgangssignale s (status) und v (valid).

Über den Arbiter soll der Zugriff von zwei Einheiten  $E_0$  und  $E_1$  auf eine gemeinsame Resource geregelt werden. Will eine Einheit die Erlaubnis für den Zugriff auf die Resource erhalten, so setzt sie ihre Request-Leitung  $(r_0$  bzw.  $r_1)$  auf 1. Der Arbiter setzt daraufhin zur nächsten aktiven Taktflanke den Valid-Ausgang v auf 0 und den Status-Ausgang auf 0 oder 1, entsprechend der Nummer der anfordernden Einheit. Mit der nächsten aktiven Taktflanke wird dann der Valid-Ausgang wieder auf 1 gesetzt (maximale Dauer von v=0 ist eine Taktperiode). Nach diesem Zeitpunkt werden auch wieder Änderungen an den Request-Eingängen (mit der nächsten Taktflanke) berücksichtigt. Sollten beide Request-Eingänge gleichzeitig gesetzt werden, so ist der Anforderung mit der niedrigsten Nummer der Vorzug geben. Nach dem Reset sollen v=1 und s=0 sein.

- a) Zeichnen Sie ein Blockschaltbild des Arbiters und der beiden Anforderungseinheiten, wobei der Arbiter als Black Box mit allen Ein- und Ausgangssignalen zu zeichnen ist.

- b) Geben Sie das Timing eines Anforderungszyklus mit allen Ein- und Ausgangssignalen des Arbiters an, wobei die Realisierung mit positiv flankengetriggerten Flip-Flops angenommen werden soll.

- c) Geben Sie die Zustandsübergangstabelle und den Zustandsübergangsgraphen des Arbiters an.

- d) Realisieren Sie den Automaten mit D-Flip-Flops.

# 2. Mealy-Automaten

# 2.1. Zweistelliger Binärzähler mit Übertragsausgang

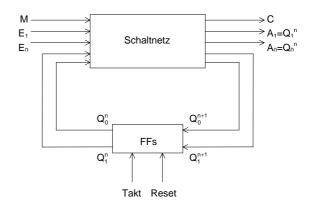

Es ist ein zweistelliger Binärzähler zu entwerfen, der die Zustände  $00,\,01,\,10,\,11,\,00,\,01$  ... zyklisch durchläuft. Der Zähler kann durch den Moduseingang M und die Setzeingänge  $E_0$  und  $E_1$  in einen definierten Anfangszustand gebracht werden. Ist M=1, so werden bei der nächsten Taktflanke die Zustände von  $E_0$  und  $E_1$  in die beiden Flip-Flops (Ausgänge  $Q_0$  und  $Q_1$ ) übernommen. Für M=0 wird der Zählerstand bei jeder Taktflanke um 1 erhöht.

Um den Zähler erweitern zu können, besitzt dieser einen Übertragsausgang C. Er soll im Zählmodus (M = 0) bei Zählerstand 11 gleich 1 sein und ist ansonsten 0. Die zweite und die weiteren Zählerstufen eines erweiterten Zählers müßten den C-Ausgang der ersten Zählerstufe auch als Eingang enthalten. In diesem Beispiel soll nur die erste Zählerstufe (also ohne C-Eingang) entworfen werden.

- a) Zeichnen Sie ein Blockschaltbild der Zählers bestehend aus Schaltnetz (Black Box), Flip-Flops und allen Eingangs- und Ausgangssignalen.

- b) Geben Sie die Übergangstabelle der Zählers an.

- c) Zeichnen Sie den Zustandsgraphen des Zählers.

- d) Bestimmen Sie die Lösungsfunktion D<sub>1</sub> für die Realisierung mit einem D-FF.

- e) Bestimmen Sie die Lösungsfunktionen  $J_1$  und  $K_1$  für die Realisierung mit einem JK-FF durch Koeffizientenvergleich.

- f) Bestimmen Sie die Lösungsfunktionen  $J_1$  und  $K_1$  für die Realisierung mit einem JK-FF direkt aus dem KV-Diagramm.

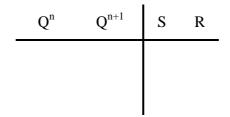

- g) Geben Sie die charakteristische Gleichung für das RS-FF an und ergänzen Sie die folgende Tabelle:

- h) Bestimmen Sie die Lösungsfunktionen R<sub>1</sub> und S<sub>1</sub> für die Realisierung mit einem RS-FF.

- i) Warum ist zur Bestimmung der Lösungsfunktionen für ein RS-FF kein Koeffizientenvergleich, wie beim JK-FF möglich?

- j) Woran sehen Sie, daß es sich bei diesem Automaten um einen Mealy-Automaten handelt?

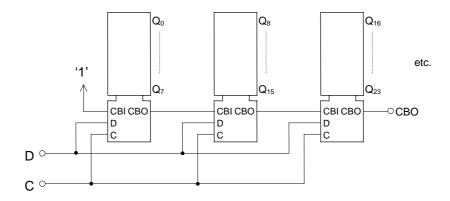

## 2.2. Up/Down Counter

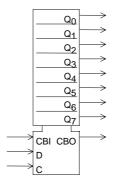

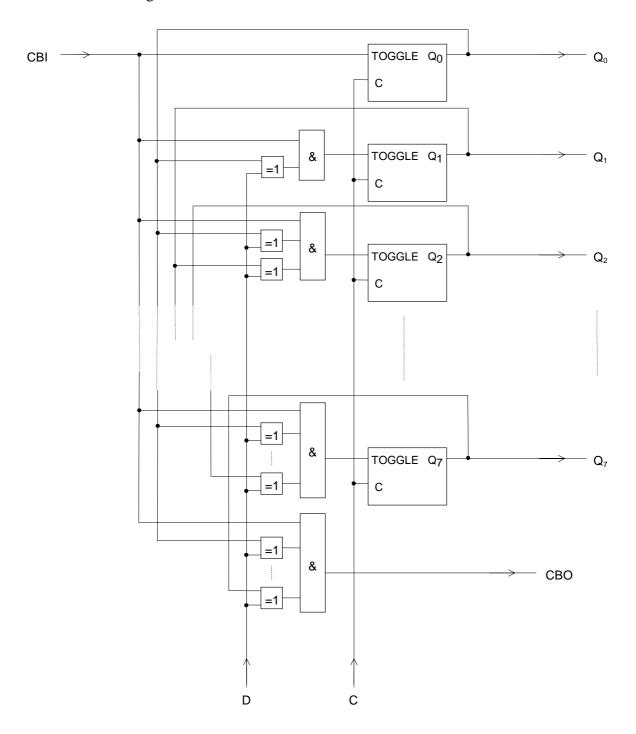

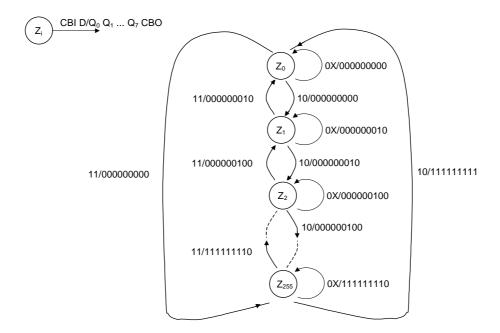

Es ist ein synchroner 8-Bit Up/Down Counter zu entwerfen. Der Zähler soll einen Carry/Borrow Ein- und Ausgang (CBI, CBO, aktiv high), einen Directioneingang (D, D = 0 entspricht Up, D = 1 entspricht Down), 8 Ausgänge für den Zählerstand (Q0..Q7) und einen Clockeingang (C) besitzen.

- a) Zeichnen Sie ein Blockschaltbild des Zählers (Black Box) mit den Eingängen links und den Ausgängen rechts.

- b) Skizzieren Sie, wie mehrere 8-Bit Zähler zu einem größeren Zähler kaskadiert werden können.

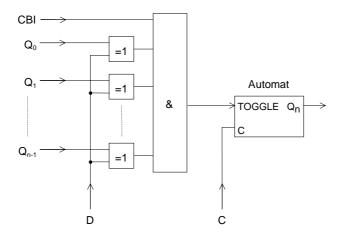

- c) Entwickeln Sie die Schaltung des 8-Bit Zählers. Der Zähler ist modularisierbar! Überlegen Sie sich wie man die einzelnen Stellen des Zählers aus möglichst gleichartigen Modulen zusammensetzen kann. Die Schaltung jeder Stelle des Zählers kann durch einen Automat, welcher für alle Stellen des Zählers gleich ist, sowie durch zusätzliche kombinatorische Logik zusammengesetzt werden. Geben Sie das Schaltbild des gesamten Zählers an, wobei der Automat als Black Box gezeichnet wird.

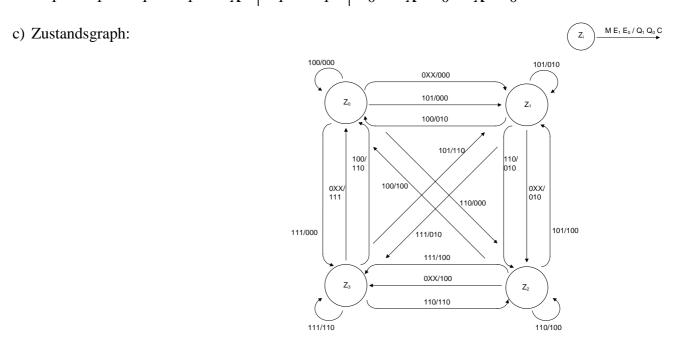

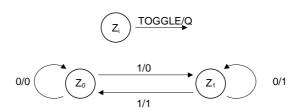

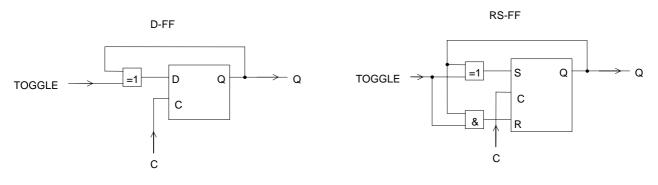

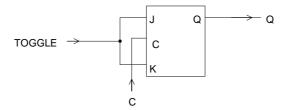

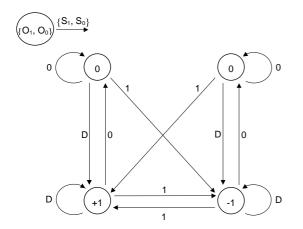

- d) Bestimmen Sie Zustandsgraph und Zustandsübergangstabelle des Automaten einer Zählstelle.

- e) Geben Sie die Gleichungen für die Realisierung des Automaten einer Zählstelle an. Welchen Automatentyp (Moore oder Mealy) stellt der Automat einer Zählstelle dar?

- f) Zeichnen Sie das Schaltbild des Automaten.

- g) Versuchen Sie den 8-Bit Zähler als einen einzigen großen Automaten mit den Eingängen CBI und D sowie den Ausgängen Q0 bis Q7 und CBO zu entwickeln. Skizzieren Sie den Zustandsgraphen des Automaten und begründen Sie, warum solch eine Vorgangsweise nicht sinnvoll ist.

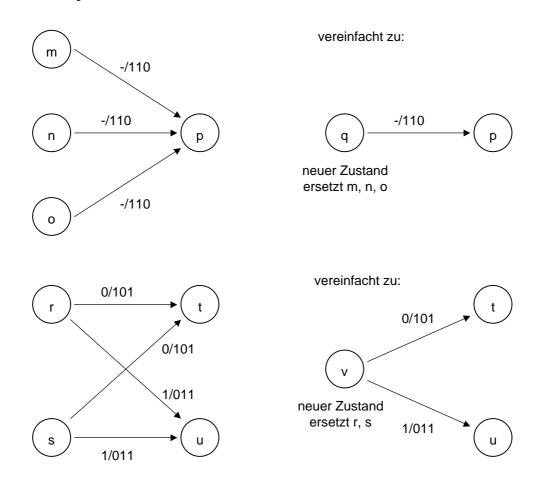

# 2.3. Vereinfachung von Zustandsgraphen

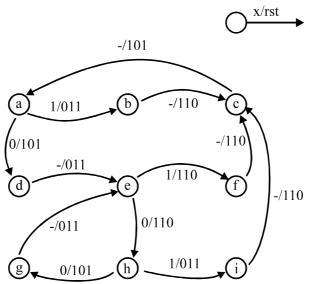

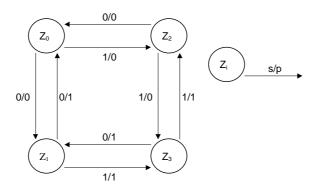

Aus dem untenstehenden Zustandsgraphen soll ein synchrones Schaltwerk in Form eines Mealy-Automaten entwickelt werden. Bei der Erstellung des Zustandsgraphen wurden redundante Zustände nicht beachtet.

- a) Geben Sie den Zustandsgraphen in Listenform an. Ordnen Sie die Zeilen der Liste nach den Zuständen  $Z^n$  und geben Sie Eingangsgröße, Ausgangsgröße und nächsten Zustand  $Z^{n+1}$  an.

- b) Formulieren Sie eine allgemeine Regel zur Vereinfachung dieser Zustandsliste durch Zusammenfassen von Zuständen. Die Funktion des Schaltwerks soll dabei vollständig unverändert bleiben.

- c) Wenden Sie diese Regel auf die Zustandsliste an und zeichnen Sie den vereinfachten Zustandsgraphen. Zusammengefaßte Zustände sind durch einen neuen Buchstaben zu bezeichnen.

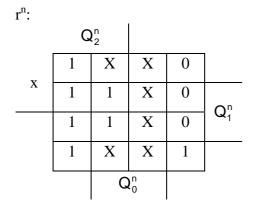

- d) Wie viele Flip-Flops sind zur Realisierung des Automaten notwendig? Wählen Sie eine Zustandscodierung, sodaß die Gleichungen für r, s und t jeweils nur zwei disjunktive Terme enthalten.

- e) Bestimmen Sie die Gleichungen für r, s und t mit der Hilfe von KV-Diagrammen, wobei Sie die gewählte Zustandscodierung aus Punkt d) zugrunde legen.

- f) Bestimmen Sie die Lösungsgleichungen für eine Realisierung mit D-FFs.

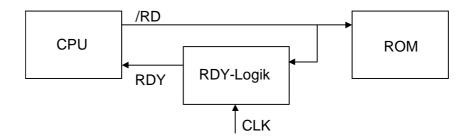

## 2.4. Ready-Logik

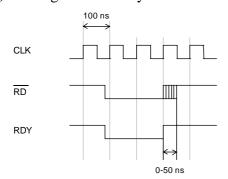

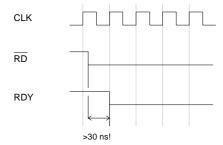

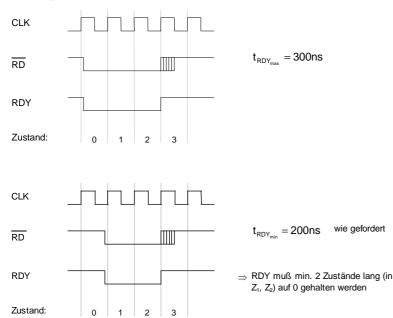

Ein schneller Prozessor soll mit einem langsamen ROM verbunden werden. Der Lesezyklus, währenddessen der Prozessor das /RD-Signal auf 0 setzt, kann durch den RDY-Eingang des Prozessors verlängert werden. Das RDY-Signal muß dazu vom Ruhezustand 1 spätestens 30 ns nach der fallenden Flanke des /RD-Signals ebenfalls auf 0 gehen. 0 ns bis 50 ns nach der steigenden Flanke des RDY-Signals beendet der Prozessor den Lesezyklus und setzt das /RD-Signal wieder auf 1. Nach der steigenden Flanke des /RD-Signals erfolgt der nächste Lesezyklus vom Prozessor frühestens wieder nach 70 ns.

Die RDY-Logik ist als synchroner Automat mit D-Flip-Flops zu realisieren. Die Taktfrequenz des Taktes CLK der RDY-Logik beträgt 10 MHz und ist unabhängig vom Prozessortakt. Die Flip-Flops schalten bei der positiven Taktflanke. Das ROM verlangt eine minimale Dauer des /RD-Impulses von 200 ns. Es ist außerdem zu beachten, daß die Zeitdauer während der RDY = 0 ist, im Hinblick auf die Performance des Systems so kurz wie möglich sein soll. Die Bauelemente der RDY-Logik können als verzögerungsfrei angenommen werden (ideale Bauelemente).

- a) Geben Sie das Timing eines Lesezyklus für die Signale /RD, RDY und CLK an. Zeitbereiche mit unbestimmtem Signalzustand sind dabei zu schraffieren.

- b) Warum kann für die RDY-Logik kein Moore-Automat verwendet werden?

- c) In welchem Zeitbereich  $t_{RDYmin}$  bis  $t_{RDYmax}$  ist RDY = 0?

- d) Geben Sie den Zustandsgraphen der RDY-Logik an. Kennzeichnen Sie im Timing-Diagramm, welcher Zeitbereich welchem Zustand des Automaten entspricht.

- e) Leiten Sie aus dem Zustandsgraphen die Zustandsübergangstabelle ab. Codieren Sie die Zustände so, daß bei Verwendung von realen Bauelementen das Ausgangssignal RDY des Automaten frei von Hazards ist.

- f) Geben Sie die zur Realisierung des Automaten erforderlichen Gleichungen an. Sie müssen dafür nicht extra ein KV-Diagramm zeichnen.

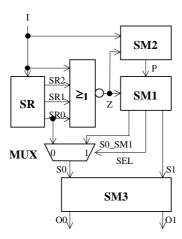

#### 2.5. HDB3-Encoder

Es soll ein Encoder realisiert werden, welcher einen seriellen NRZ-Datenstrom in einen HDB3-codierten Datenstrom umwandelt. Der Encoder besitzt den Eingang I (Eingang für NRZ-Daten), den 2-Bit-Ausgangsvektor {O0, O1} (Ausgang der HDB3-codierten Daten), ein Takt- und ein Resetsignal (das Taktsignal und das Resetsignal wurden der Übersichtlichkeit halber nicht in das folgende Schaltbild eingezeichnet).

Funktionell läßt sich die Codierung in zwei aufeinanderfolgende Schritte zerlegen, wobei die Codierungsvorschrift für die beiden Schritte folgendermaßen lautet:

Im ersten Schritt wird aus dem seriellen NRZ-Datenstrom am Eingang I, ein Zwischensignal am Vektor {S0, S1} erzeugt. Dabei wird eine 1 am Eingang I ebenfalls auf eine 1 am Zwischensignal {S0, S1} abgebildet. Eine 0 am Eingang I wird, solange die 3 vorhergehenden Bits am Eingang I nicht ebenfalls 0 waren, auf eine 0 am Zwischensignal abgebildet. Ein Block von 4 aufeinanderfolgenden Nullen wird durch eines der beiden Ersatzmuster 100D oder 000D ersetzt. Das Ersatzmuster 100D wird substituiert, wenn seit dem letzten Ersatzmuster eine gerade Zahl von Einsen an I aufgetreten ist. Das Ersatzmuster 000D wird verwendet, wenn seit dem letzten Ersatzmuster eine ungerade Zahl von Einsen an I aufgetreten ist. Das Zwischensignal {S0, S1} wird von der Schaltung durch die Automaten SM1 und SM2, das Schieberegister SR, das NOR-Gatter und den Multiplexer MUX erzeugt.

Im zweiten Schritt wird aus dem Zwischensignal der HDB3-Code erzeugt und am Ausgangsvektor {00, 01} ausgegeben. Eine 0 am Zwischensignal wird ebenfalls auf eine 0 am Ausgang abgebildet. Eine 1 am Zwischensignal wird abwechselnd in +1 und -1 am Ausgang abgebildet. Das mit D bezeichnete Bit am Zwischensignal wird in +1 und -1 abgebildet, aber so, das die Bipolar-Regel der

abwechselnden +1 und -1 verletzt wird. Das Ausgangssignal an {O0, O1} wird in der Schaltung vom Automaten SM3 aus dem Zwischensignal {S0, S1} erzeugt.

#### Beispiel:

```

Eingangssignal I: ... 11011 0000 01 0000 0000 101 0000 ... Zwischensignal \{S0, S1\}: ... 11011 100D 01 000D 100D 101 100D ... Ausgangssignal \{00, O1\}: ... +-0+- +00+ 0- 000- +00+ -0+ -0+ ...

```

Die Werte +1 und -1 wurden in obigem Beispiel durch + und - dargestellt. Kurz nach jeder positiven Taktflanke wird ein neues Bit an I angelegt. Der Zeitversatz zwischen den Signalen I,  $\{S0, S1\}$  sowie  $\{O0, O1\}$ , welcher durch die Schaltung bedingt ist, wird in der Darstellung des obigen Beispiels nicht berücksichtigt. Die Codierung der Vektoren  $\{S0, S1\}$  und  $\{O0, O1\}$  erfolgt laut folgenden Tabellen:

| S1 | S0 | entspricht |

|----|----|------------|

| 0  | 0  | 0          |

| 0  | 1  | 1          |

| 1  | X  | D          |

| 01 | O0 | entspricht |

|----|----|------------|

| 0  | X  | 0          |

| 1  | 0  | -1         |

| 1  | 1  | +1         |

Mit jeder positiven Taktflanke wird das Schieberegister SR um eine Stelle weiter geschoben, d.h.: I→SR2, SR2→SR1, SR1→SR0. Der Ausgang S0 des Multiplexers MUX wird bei SEL=0 mit dem Eingang 0 verbunden und bei SEL=1 mit dem Eingang 1 verbunden. Der Automat SM2 soll an seinem Ausgang P (Parity) eine 1 ausgeben, wenn seit dem letzten Ersatzmuster eine gerade Anzahl von Einsen aufgetreten ist. Wenn seit dem letzten Ersatzmuster eine ungerade Anzahl von Einsen aufgetreten ist, soll hingegen eine 0 an P ausgegeben werden. Alle 3 Automaten sollen mit positiv flankengetriggerten Flip-Flops realisiert werden. Die Resetzustände der Automaten und des Schieberegisters können in diesem Beispiel unberücksichtigt bleiben.

- a) Geben Sie den Zustandsgraphen des Automaten SM1 an. Erklären Sie die Funktion der Schaltung um den Automaten SM1 (Schieberegister SR, NOR-Gatter und Multiplexer MUX). Muß der Automat als Moore-Automat oder als Mealy-Automat realisiert werden oder ist dies egal?

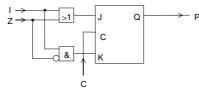

- b) Geben Sie die Schaltung des Automaten SM2 an. Muß der Automat als Moore-Automat oder als Mealy-Automat realisiert werden oder ist dies egal?

- c) Geben Sie den Zustandsgraphen des Automaten SM3 an wobei Sie den Automaten als Moore-Automat realisieren sollen.

- d) Wie groß ist der zeitliche Versatz zwischen den Signalen I, {S0, S1} und {O0, O1} in Taktperioden?

- e) Stellt die Gesamtschaltung des HDB3-Encoders eines Mealy- oder einen Moore-Automaten dar?

- f) Wie viele Flip-Flops werden für den gesamten HDB3-Encoder benötigt? Benötigt die Schaltung des HDB3-Encoders mehr oder weniger Bauteile, wenn der gesamte Encoder als ein einziger großer Automat realisiert wird?

# 3. Programmschaltwerke

## 3.1. Programmschaltwerk für Drehstromsignal

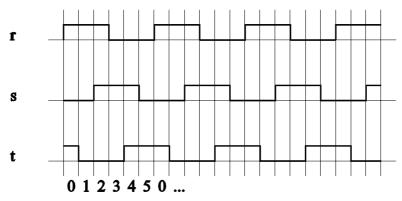

Ein fiktiver Wechselrichter soll Gleichspannung aus einer Pufferbatterie in Drehstrom umwandeln. Als Steuersignale für die Wechselrichtung benötigt er die Signale r, s und t mit folgender Signalform:

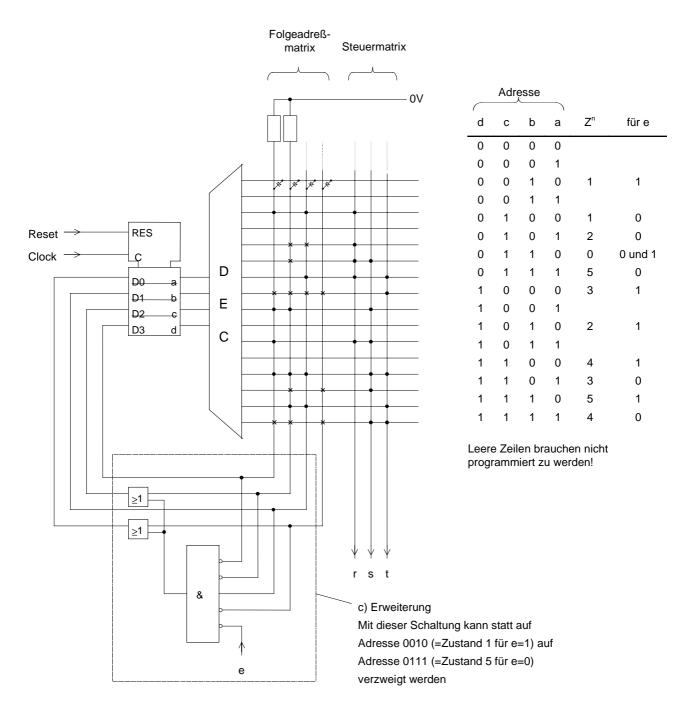

Es lassen sich 6 unterschiedliche Zustände der Ausgänge r, s und t unterscheiden, die zyklisch durchlaufen werden. Der Umlaufsinn des Drehstroms soll umkehrbar sein. Abhängig vom Steuereingang e (Drehsinn) soll das Programmschaltwerk für e = 1 die Folge 0123450123.. und für e = 0 die Folge 0543210543.. an den Ausgängen r, s und t der Steuermatrix ausgeben. Der Drehsinn läßt sich nur im Zustand 0 umkehren. Um Hazards zu vermeiden, werden die Zustände des Schaltwerks im Gray-Code durchlaufen. Verwenden Sie folgende Zuordnung:

- a) Geben Sie das Schaltbild des Programmschaltwerks an, das aus den Elementen Folgeadreßregister (D-FF), Dekoder, Folgeadreßmatrix und Steuermatrix besteht.

- b) Ergänzen Sie die Diodenbrücken in der Folgeadreßmatrix für e = 1 (nur Drehrichtung 0123..). Zeichnen Sie für einen Kreuzungspunkt die exakte Beschaltung (Widerstände, Dioden) neben die Matrix. Für die restlichen Verbindungen in der Matrix reicht es einen Punkt an der entsprechenden Stelle zu machen.

- c) Erweitern Sie die Schaltung durch Verwendung eines 5-fach-UND-Gatters und weiterer Gatter derart, daß im Zustand 0 für e = 0 auf den Zustand 5 und nicht auf den Zustand 1 verzweigt wird (Schaltung für zwei Drehrichtungen). Die Erweiterung erfolgt an zwei Leitungen die von der Folgeadreßmatrix zu den FF-Eingängen führen. Stammen vier der fünf Leitungen am UND-Gatter vom Ausgang oder vom Eingang der Folgeadreßmatrix? Ergänzen Sie die benötigten

Verbindungen in der Folgeadreßmatrix, wobei Sie zur Unterscheidung der beiden Drehrichtungen diesmal Kreuze statt Punkte machen.

- d) Ergänzen Sie die Verbindungen in der Steuermatrix für die Erzeugung der Signale r, s und t.

- e) Welche Bauteile des Programmschaltwerks entsprechen dem Program Counter, dem ROM und dem Befehlsdekoder eines Programmschaltwerks bzw. Mikrocontrollers im allgemeinen Sinn? Welche Befehle können vom Programmschaltwerk abgearbeitet werden?

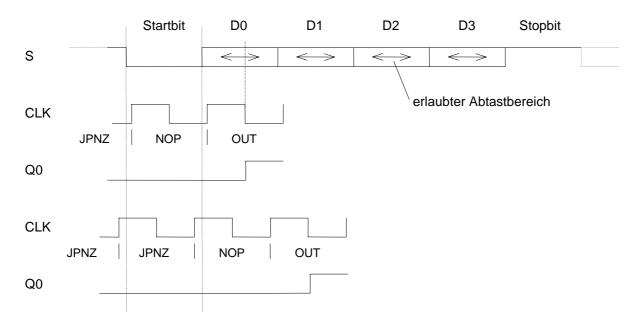

## 3.2. Anzeigeeinheit für seriell übertragene Daten

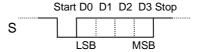

Über eine serielle Datenleitung S werden Nibbles (4-bit Worte) an eine Anzeigeeinheit übertragen. Nach dem Startbit (= 0) folgen die Datenbits in aufsteigender Reihenfolge (d.h.  $D_0$  zuerst). Durch ein Stopbit (= 1) wird die Übertragung abgeschlossen. Der Ruhezustand der seriellen Leitung ist 1.

Das vollständig empfangene Nibble (Ausgabe erst nach Abschluß des Empfangs) wird von der Anzeigeeinheit über vier Lampen angezeigt, die mit den Steuerleitungen  $L_0$  bis  $L_3$  entsprechend den Datenbits  $D_0$  bis  $D_3$  angesteuert werden.

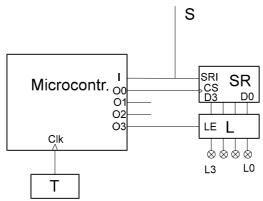

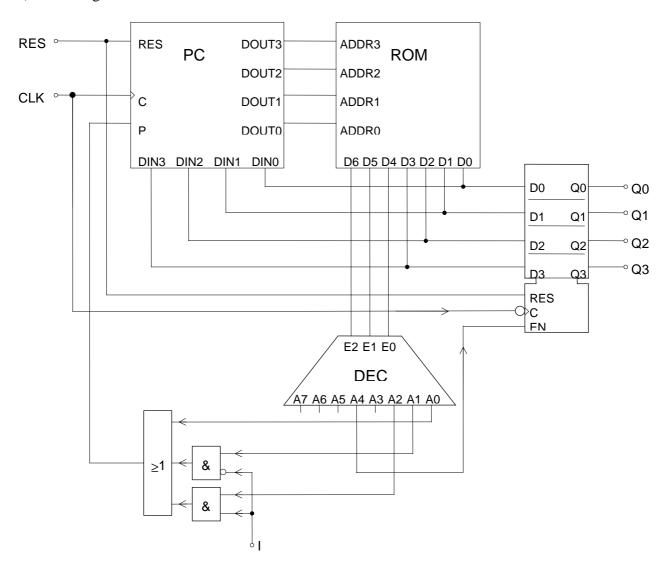

Die Anzeigeeinheit besteht aus zwei Empfangsregistern (Schieberegister SR und Latch L) und einem Microcontroller, der die Taktsignale für die beiden Empfangsregister aus dem seriellen Datenstrom am Eingang I berechnet.

Das Schieberegister SR besteht aus einer Kette von 4 D-Flip-Flops die gemeinsam durch eine positive Flanke am Takteingang CS getriggert werden. Der serielle Eingang des Schieberegisters heißt SRI (Eingang des höchstwertigsten D-FF) und die Ausgänge heißen D<sub>0</sub> bis D<sub>3</sub>. Die Daten werden vom höchstwertigsten zum niederwertigsten Bit des Schieberegisters (also nach rechts) geschoben. Das D-Latch L übernimmt die Daten an seinen Eingängen vom Schieberegister, wenn an seinem Latch-Enable-Eingang LE eine 1 anliegt.

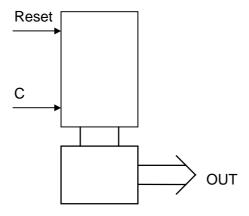

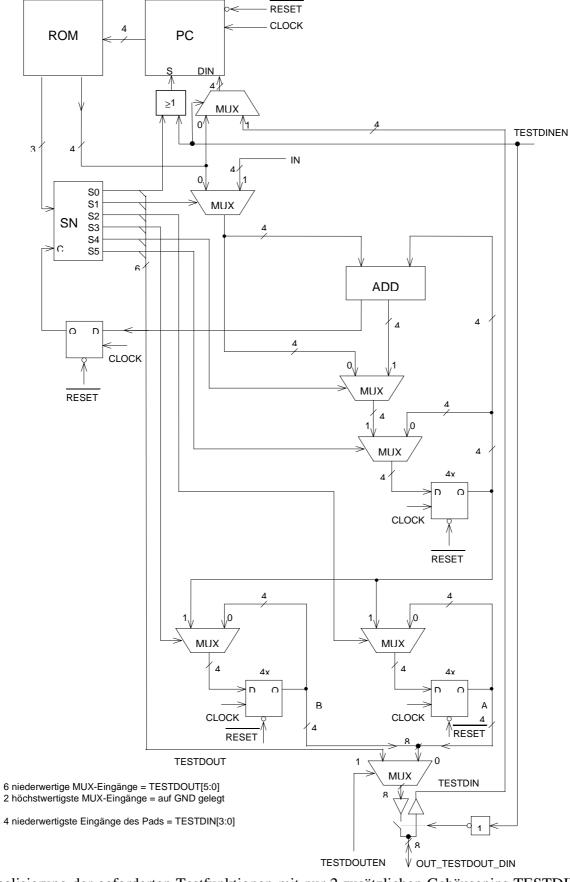

Der Microcontroller besitzt ein 1-Bit-Eingangsport I und ein 4-Bit-Ausgangsport O<sub>0</sub> bis O<sub>3</sub>. Er generiert mit Hilfe des im internen ROM abgelegten Codes aus dem am Eingangsport I anliegenden seriellen Datenstrom die Taktsignale für die beiden Empfangsregister SR und L an seinem Ausgangsport O.

Der Microcontroller besteht im Wesentlichen aus vier Funktionsblöcken:

- 1.) Program Counter PC: Synchroner 4-Bit Zähler mit Preseteingang P. Mit P = 1 wird der Zählerstand vom Eingang übernommen, mit P = 0 wird der Counter inkrementiert. Die Übernahme des neuen Zählerstandes an die Ausgänge erfolgt bei der positiven Taktflanke.

- 2.) ROM: 4 Adreßeingänge, 7 Datenausgänge, die unteren 4 Bits enthalten Daten, die oberen 3 Bits enthalten den Befehlscode.

- 3.) 1 aus n Dekoder DEC: 3 Eingänge, 8 Ausgänge, die durch den Eingang ausgewählte Ausgangsleitung ist 1, alle anderen sind 0.

- 4.) Synchrones Ausgaberegister: 4-Bit negativ flankengetriggertes Register mit Takteingang C und Enableeingang EN. Ein 4-Bit Eingangswert wird vom Register mit der negativen Taktflanke C an die Ausgänge übernommen, wenn EN = 1 ist.

Außerdem stehen noch diverse Logikgatter zur Verfügung. Der Microcontroller soll die Befehle

ausführen können. Das Hochzählen des Program Counters soll bei der positiven Flanke des Taktes Clk und das Ausgeben (Befehl OUT) bei der negativen Flanke von Clk erfolgen.

- a) Zeichnen Sie die Schaltung des Microcontrollers. Beschriften Sie alle Ein- und Ausgänge der Bausteine denen in der Angabe ein Name gegeben wurde. Geben Sie die gewählte Zuordnung der Befehlscodes (obere 3 Bits im ROM) zu den Befehlen an. Erklären Sie die Funktion des Schaltungsteils für die Abarbeitung der bedingten und unbedingten Sprungbefehle. Kennzeichnen Sie Gattereingänge durch entsprechende Pfeile.

- b) Wieviel mal (ganzzahlig) muß die Taktfrequenz des Microcontrollers größer sein als die Bitrate der seriellen Übertragung, wenn jedes Bit in der mittleren Hälfte (25% bis 75%) der Bitdauer vom Schieberegister SR eingelesen werden soll? Beachten Sie, daß der Program Counter mit der positiven Taktflanke inkrementiert wird bzw. einen neuen Zählerstand lädt, währenddessen die Datenausgabe bei der negativen Taktflanke erfolgt!

- c) Wie lautet das Assemblerprogramm für den Microcontroller? Geben Sie für jede Adresse den Zustand aller Datenbits des ROMs an. Geben Sie an, welcher Adreßbereich im ROM nicht programmiert werden muß.

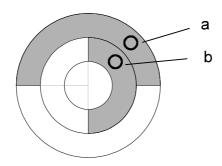

# 3.3. Programmschaltwerk zur Drehrichtungsbestimmung

Die Signale eines optischen Winkelgebers an einer Maschinenwelle sollen auf die Drehrichtung der Maschine durch ein Programmschaltwerk untersucht werden. Der Winkelgeber ist wie folgt konstruiert:

Ist das Feld schwarz, so gibt der Sensor 0 aus. Ist das Feld weiß, so gibt er 1 aus. Die Signale von b und a werden zum Eingangssignal e (b = MSB, a = LSB, Wertebereich = 0..3) zusammengefaßt.

Die Auswerteschaltung besitzt den Eingang e sowie den Ausgang a mit den Leitungen L und R (L = MSB, R = LSB, Wertebereich = 0..3), die zwei entsprechende Anzeigelampen einschalten (0 = dunkel, 1 = hell).

Bei Inbetriebnahme von Maschine und Auswerteelektronik steht die Maschine still und keine der beiden Lampen darf leuchten. Nach der ersten Vierteldrehung soll eine der beiden Lampen entsprechend der Drehrichtung eingeschaltet werden. Dreht sich die Welle bis zum nächsten Auswertezeitpunkt in die gleiche Richtung weiter oder bleibt der Winkel unverändert, so bleibt die entsprechende Anzeigelampe eingeschalten. Dreht sich die Welle um eine Vierteldrehung in die andere Richtung, so soll die Anzeige wechseln. Durch geeignete Anpassung der Abtasthäufigkeit an die maximale Maschinendrehzahl wird sichergestellt, daß sich die Welle um maximal 90° pro Abtastintervall dreht.

- a) Geben Sie die zeitliche Abfolge des Eingangssignals e in Abhängigkeit von der Drehrichtung an.

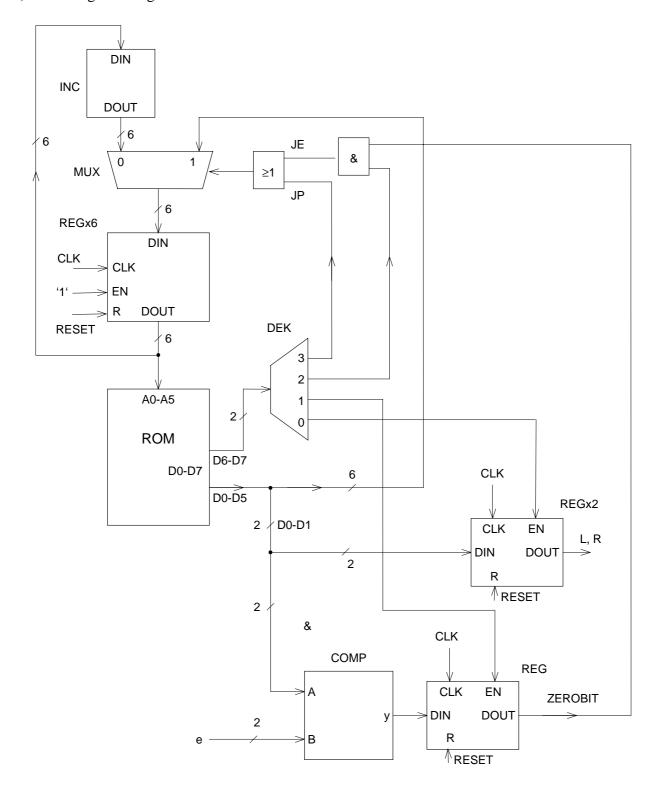

- b) Geben Sie die Schaltung eines Programmschaltwerkes mit dem Eingang e und dem Ausgang a an, das in der Lage ist, folgende Assemblerbefehle zu verarbeiten:

| Befehl | Parameter | Binärcode | Erläuterung                                                                     |

|--------|-----------|-----------|---------------------------------------------------------------------------------|

| SET    | 03        | 00xx xx   | Setzt den Ausgang a auf den angegebenen Wert                                    |

| СР     | 03        | 01xx xx   | Vergleicht e mit dem angegebenen Parameter und setzt bei Gleichheit das Zerobit |

| JE     | 063       | 10        | Springt, wenn das Zerobit gesetzt ist, auf die angegebene Adresse               |

| JP     | 063       | 11        | Springt auf die angegebene Adresse                                              |

0,1 ... vorgegeben, x ... beliebig, - ... mit Parameter belegt

Das Schaltwerk wird mit dem Taktsignal CLK versorgt. Mit einer positiven Flanke an CLK werden sowohl der Programmzähler inkrementiert bzw. mit einer Sprungadresse geladen als auch die Ergebnisse von Berechnungen (Zerobit, Ausgaberegister) in den zugehörigen Registern abgespeichert.

Als fertige Blöcke können verwendet werden: Ein Inkrementierer INC mit 6-Bit Ein- und Ausgang, ein 6 Bit breiter 2-zu-1 Multiplexer MUX, ein 64 Byte großes ROM, ein 2 x 2 Bit Komperator COMP, ein 2-zu-4 Dekoder DEK und diverse Gatter. Als speichernde Elemente sind positiv flankengetriggerte Register mit dem synchronen Enableeingang EN zu verwenden (der Wert am Eingang des Registers wird mit der positiven Flanke des Takteingangs CLK an den Ausgang des Registers übernommen, wenn EN zu diesem Zeitpunkt 1 ist). Über den Reset-Eingang kann der Ausgang des Registers beim Reset auf 0 gesetzt werden.

- c) Wie lautet die absolute Reset-Adresse des Schaltwerks?

- d) Geben Sie ein Programm für das entworfene Schaltwerk in der Form

[Adresse:] Opcode Parameter ; Erläuterung

an, das in der Lage ist die geforderten Funktionen zu erfüllen. Verwenden Sie der Einfachheit halber symbolische Adressen.

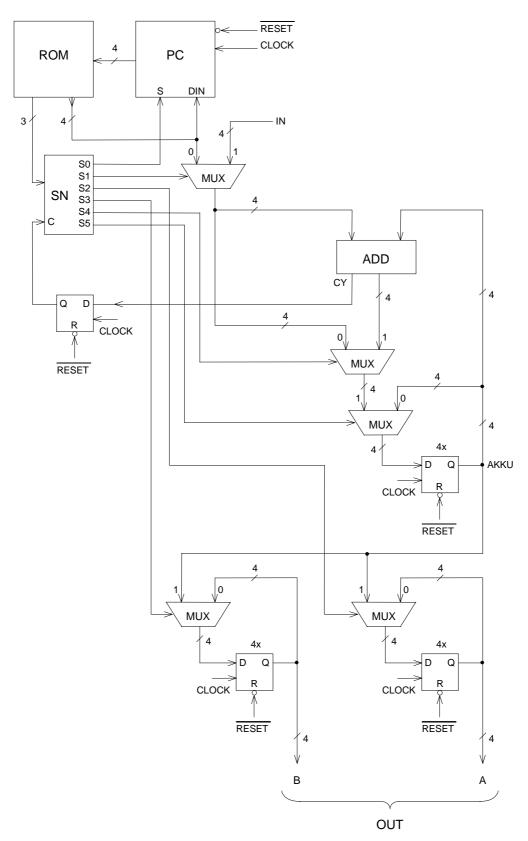

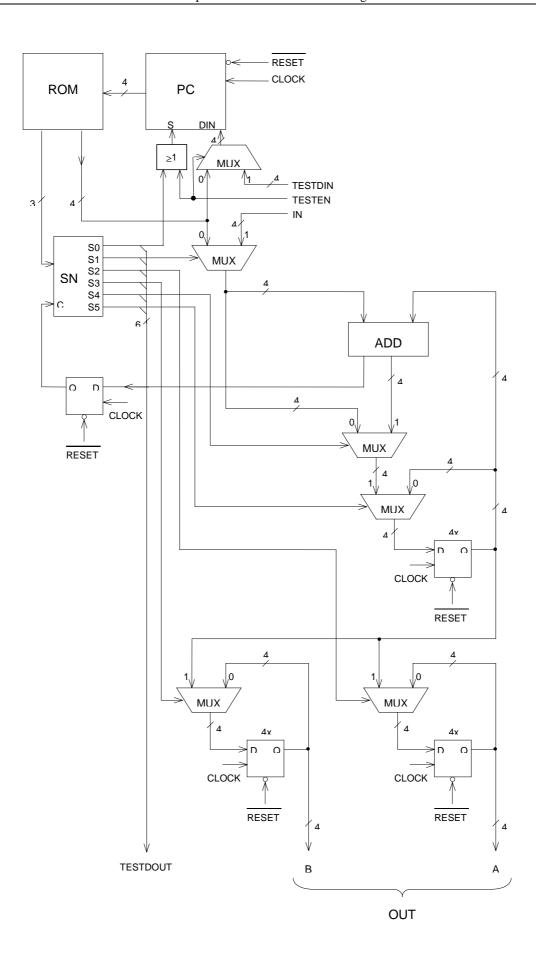

## 3.4. Programmschaltwerk mit Addierer

Es ist ein Programmschaltwerk zu entwerfen, welches nach dem Reset eine Binärzahl vom 4 Bit breiten Eingang IN einliest, die Zahl 5 dazu addiert und das Ergebnis am 8 Bit breiten Ausgangsport OUT ausgibt. Danach soll das Schaltwerk keine Veränderung an den Ausgängen mehr durchführen.

Die zur Verfügung stehenden Bausteine sind:

- Programm Counter PC: Ladbarer synchroner 4-Bit-Zähler (zählt bei positiver Taktflanke), low-aktiver Reset-Eingang, Steuereingang S (S = 0 count, S = 1 load).

- 16x7 Bit großes ROM

- 4-Bit-Volladdierer ADD: Zwei 4 Bit breite Eingänge, ein 4 Bit breiter Ausgang, Carryausgang CY

- Multiplexer MUX: Zwei Eingänge, ein Ausgang, Steuereingang S zur Umschaltung zwischen den beiden Eingängen, die beiden Eingänge sind mit 0 und 1 (entsprechend Steuereingang S) zu beschriften.

- D-Flip-Flops in den Breiten 4 Bit und 1 Bit (OUT wird durch zwei getrennt gesteuerte 4-Bit-D-Flip-Flops realisiert) mit low-aktivem Reset-Eingang.

- Schaltnetz SN des Steuerwerks als Black Box (Block mit Ein- und Ausgangsleitungen ohne Innenschaltung). Die Übertragungsfunktion des Schaltnetzes wird in Punkt b) in Tabellenform angegeben.

Das Schaltwerk besitzt den Takteingang CLOCK sowie einen low-aktiven Reset-Eingang. Der Befehlssatz, den das Schaltwerk ausführen kann, lautet:

IN ladet Akku mit Zahl am Eingangsport IN

CONST Zahl ladet Akku mit angegebener Zahl

ADDI addiert Zahl am Eingangsport IN zum Akku

ADDC Zahl addiert angegebene Zahl zum Akku

OUTa gibt Akku auf Ausgangsport OUTa aus

| OUTb |      | gibt Akku auf Ausgangsport OUTb aus                                               |

|------|------|-----------------------------------------------------------------------------------|

| JMP  | Zahl | PC springt auf durch Zahl angegebene Adresse                                      |

| JC   | Zahl | Sprung auf durch Zahl angegebene Adresse, wenn Carryausgang von ADD logisch 1 ist |

- a) Zeichnen Sie das Schaltbild des beschriebenen Programmschaltwerks unter Verwendung der angegebenen Bauteile. Die Taktsignale müssen direkt an die Takteingänge der Bausteine gelegt werden (keine Verknüpfung über Inverter oder Gatter)! Die bedingten Aktionen werden durch Multiplexer vor den Eingängen der FFs realisiert. Alle getakteten Bauelemente sind mit der extern zur Verfügung gestellten Resetleitung zu verbinden. Durch den Reset werden alle angeschlossenen Bausteine auf 0 gesetzt. Für Busse sollen nur Striche mit Breitenangabe eingezeichnet werden.

- b) Geben Sie die Wahrheitstabelle für das Schaltnetz SN des Steuerwerkes an.

- c) Geben Sie ein Programm für das entworfene Schaltwerk in der Form

[Adresse:] Opcode Parameter ; Erläuterung

an, das in der Lage ist die geforderten Funktionen zu erfüllen. Verwenden Sie der Einfachheit halber symbolische Adressen.

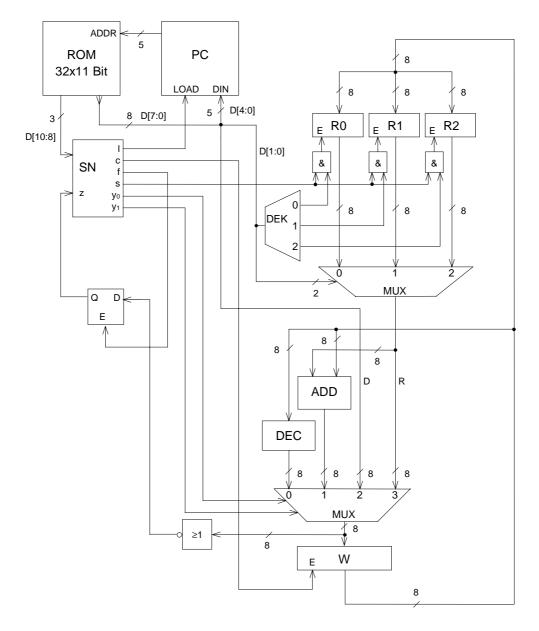

## 3.5. Multiplizierer

Es ist ein autonomes Programmschaltwerk zu entwerfen, welches in der Lage ist, einen Multiplikanden n mit einem Multiplikator m durch m-maliges addieren von n zu multiplizieren und das Ergebnis auf dem Bus OUT auszugegeben.

Das Programmschaltwerk ist eine 1-Operanden-Maschine mit dem Arbeitsregister W und den Hilfsregistern  $R_0$ ,  $R_1$  und  $R_2$ . Es kennt folgende Befehle:

| SET | konst | Laden von W mit der Konstanten konst                       |

|-----|-------|------------------------------------------------------------|

| LD  | Ri    | Laden von W mit dem Register R <sub>i</sub>                |

| STR | $R_i$ | Speichern von W in das Register R <sub>i</sub>             |

| ADD | $R_i$ | Addieren des Registers R <sub>i</sub> zu W                 |

| DEC | •     | Dekrementieren von W um 1                                  |

| JNZ | Adr   | Bedingter Sprung auf Adresse Adr wenn Zeroflag $Z = 0$ ist |

JMP Adr Unbedingter Sprung auf Adresse Adr

Das Zeroflag Z soll nur durch die beiden Befehle SET konst und DEC beeinflußt werden.

a) Geben Sie das Programm für eine Multiplikation an. In R<sub>0</sub> ist der Multiplikand n, in R<sub>1</sub> der Multiplikator m und in R<sub>2</sub> das Ergebnis der Multiplikation abzulegen. Initialisieren Sie die Register mit den erforderlichen Werten, berechnen Sie in einer Schleife das geforderte Produkt und lassen Sie das Programm in einer Endlosschleife am Programmende enden. Die Konstanten n und m sind vom Typ unsigned integer und immer so klein, daß ihr Produkt ohne Überlauf in die Register paßt. Verwenden Sie der Einfachheit halber für die Konstanten und die Adressen symbolische Namen.

Das Programmschaltwerk besteht aus den drei Teilen Operatorblock, Operandenblock und Steuerwerk zerlegt.

Der Operatorblock enthält das Arbeitsregister W, die Logik für das Zeroflag, den Addierer ADD (Black Box), den Dekrementierer DEC (Black Box) sowie einen 4-zu-1-Busmultiplexer, der auswählt, mit welchem Wert das Arbeitsregister W geladen wird. Der Operatorblock besitzt als Eingang unter anderem den Bus R vom Operandenblock und den Datenbus D vom ROM.

Der Operandenblock enthält einen Dekoder DEK, der auswählt, welches Register geschrieben werden soll, die drei Register R<sub>i</sub> und einen 3-zu-1-Busmultiplexer, der auswählt, welches Register dem Operatorblock über den Bus R zur Verfügung gestellt wird.

Das Steuerwerk enthält den ladbaren Program Counter PC, das ROM in erforderlicher Größe und das Schaltnetz des Steuerwerks SN (Black Box). Die Wahrheitstabelle des Schaltnetzes SN wird in Punkt c) in Tabellenform angegeben. Es sind unter anderem die Steuersignale c (Compute, 1 wenn W sich verändern soll), f (Flag, 1 wenn Zero-Flag sich verändern soll), s (Store, 1 wenn sich ein Register  $R_i$  verändern soll) und  $y_0$  und  $y_1$  (Auswahl des nächsten in W zu ladenden Werts) zu verwenden. Die Auswahl der Register  $R_i$  erfolgt über die beiden niederwertigsten Bits des Datenbusses D.

Das ganze Programmschaltwerk wird mit dem globalen Taktsignal C getaktet. Alle Register, Flip-Flops und der Program Counter werden über ein globales Resetsignal resetiert.

Alle Busse sind nur als einzelne Linien mit Breitenangabe auszuführen. Die Bauelemente können als einfache Kästchen gezeichnet werden. Als speichernde Elemente sind positiv flankengetriggerte Register mit dem synchronen Enableeingang E zu verwenden (der Wert am Eingang des Registers wird mit der positiven Flanke des Takteingangs an den Ausgang des Registers übernommen, wenn E zu diesem Zeitpunkt 1 ist). Bei Multiplexern und Dekodern sind die Anschlüsse zu numerieren. Die Register W und R<sub>i</sub> besitzen eine Breite von 8 Bit. Für das ROM ist die Breite von Adreß- und Datenbus anzugeben. Die Signalrichtungen sind durch Pfeile zu markieren. Die angegebenen Bauteile und Interfaces sind **nicht** vollständig.

- b) Geben Sie das Schaltbild des Schaltwerks an.

- c) Geben Sie die Wahrheitstabelle für das Schaltnetz SN des Steuerwerks an.

# 4. Hardwarebeschreibungssprachen

## 4.1. Beschreibung von Multiplexern in VHDL

Im Rahmen dieses Beispiels sollen verschiedene Typen von Multiplexern in VHDL implementiert werden.

Aus welchem Zeichenvorrat setzen sich VHDL-Identifier zusammen? Geben Sie eine allgemeine Regel an.

- a) Wie werden in VHDL Kommentare gekennzeichnet?

- b) Was genau wird durch eine Entity bzw. eine Architecture beschrieben? Welche Abhängigkeit besteht zwischen Entity und Architecture?

- c) Geben Sie die Entity für einen 2-zu-1-Multiplexer an, der jeweils eines der beiden Signale IN0 und IN1 in Abhängigkeit des Steuersignals SEL (IN0 für SEL = 0, IN1 für SEL = 1) an den Ausgang OUTMUX multiplext. Erklären Sie den Aufbau der Entity und der dabei verwendeten Statements.

- d) Geben Sie eine Architecture an, die die Funktionalität des in Punkt d) beschriebenen 2-zu-1-Multiplexers implementiert. Der Multiplexer soll dabei durch eine bedingte Signalzuweisung (mittels *when*) realisiert werden. Erklären Sie den Aufbau der Architecture und der dabei verwendeten Statements.

- e) Wie lauten in VHDL die Operatoren für die boolschen Funktionen Negation, UND, ODER und Exklusiv-ODER?

- f) Geben Sie eine Architecture an, die die Funktionalität des in Punkt d) beschriebenen 2-zu-1-Multiplexers implementiert. Der Multiplexer soll dabei über boolesche Operatoren realisiert werden. Erklären Sie den Aufbau der Architecture und der dabei verwendeten Statements. Auf die Angabe des Headers kann hier ausnahmsweise verzichtet werden.

- g) Geben Sie die Entity für einen 2x4-Bit-zu-1x4-Bit-Multiplexer an, der jeweils einen der beiden 4-Bit-Signalvektoren INO und IN1 in Abhängigkeit des Steuersignals SEL (INO für SEL = 0, IN1 für SEL = 1) an den 4-Bit-Ausgangsvektor OUTMUX multiplext. Auf die Angabe des Headers kann hier ausnahmsweise verzichtet werden.

# 4.2. Beschreibung von Flip-Flops und Registern in VHDL

Im Rahmen dieses Beispiels sollen verschiedene Typen von synchronen Flip-Flops und Registern in VHDL implementiert werden. Auf die Angabe des Headers kann in diesem Beispiel ausnahmsweise verzichtet werden.

a) Wie lautet die Richtlinie des Instituts zur Bezeichnung von low-aktiven Signalen? Welchen Sinn hat diese und ähnliche Richtlinien?

- b) Was ist im Rahmen von Zuweisungen an Signalvektoren zu beachten? Wie werden Konstanten an Signale vom Typ *std\_logic* und *std\_logic\_vector* zugewiesen? Was ist bei dabei zu beachten?

- c) Geben Sie die Architecture für ein positiv flankengetriggertes D-Flip-Flop an. Das Flip-Flop besitzt den Dateneingang D, den Datenausgang Q und das Taktsignal CLK. Außerdem soll das Flip-Flop noch einen low-aktiven Reseteingang besitzen, mit dem der Ausgang Q des Flip-Flops asynchron zum Taktsignal auf logisch 0 gesetzt werden kann. Ein Reset soll dabei Priorität gegenüber dem Laden des Flip-Flops über den Eingang D haben. Erklären Sie den Aufbau der Architecture und der dabei verwendeten Statements (insbesondere das *process*-Statement).

- d) Was muß in der Architecture aus Punkt c) geändert werden, um das Flip-Flop in ein negativ flankengetriggertes Flip-Flop, bzw. ein Latch das für CLK = 1 transparent ist, umzuwandeln?

- e) Geben Sie die Architecture für ein positiv flankengetriggertes 8-Bit breites Parallelregister an. Das Register besitzt den 8-Bit breiten Dateneingangsvektor D, den 8-Bit breiten Datenausgangsvektor Q, das synchrone Steuersignal LOAD, das Taktsignal CLK und das asynchrone low-aktive Resetsignal RESETB. Der 8-Bit-Wert am Eingang D soll an den 8-Bit-Ausgang Q mit der steigenden Flanke des Taktsignals CLK übernommen werden, wenn der Zustand von LOAD zu diesem Zeitpunkt logisch 1 ist. Andernfalls soll der alte Zustand Q im nächsten Takt beibehalten werden. Bei einem Reset soll der Ausgangsvektor Q des Flip-Flops asynchron zum Taktsignal auf logisch 0 gesetzt werden. Ein Reset soll dabei Priorität gegenüber dem Laden des Registers über LOAD haben. Erklären Sie den Aufbau der Architecture und der dabei verwendeten Statements.

- Geben Sie die Architecture für ein positiv flankengetriggertes 4-Bit-Schieberegister an. Das Register besitzt den seriellen Dateneingang SREGIN, den parallelen 4-Bit-Dateneingang LOADIN, den seriellen Datenausgang SREGOUT, die synchronen Steuersignale CLR, LOAD und SHIFT, das Taktsignal CLK und das asynchrone, high-aktive Resetsignal RESET. Alle 4 Stellen des Schieberegister sollen mit der steigenden Flanke des Taktsignals CLK auf 0 gesetzt werden, wenn der Eingang CLR zu diesem Zeitpunkt 1 ist. Der 4-Bit-Wert am Eingang LOADIN soll in die 4 Stellen des Schieberegisters mit der steigenden Flanke des Taktsignals CLK übernommen werden, wenn der Zustand von LOAD zu diesem Zeitpunkt logisch 1 ist. Alle 4 Stellen des Schieberegisters sollen mit der steigenden Flanke des Taktsignals CLK um eine Stelle, von der niederwertigeren zur höherwertigeren Stelle des Schieberegisters, geschoben werden, wenn der Eingang SHIFT zu diesem Zeitpunkt 1 ist. Der Wert des Eingangs SREGIN soll dabei in die niederwertigste Stelle des Schieberegisters übernommen werden. Ist mehr als eines der Signale CLR, LOAD und SHIFT logisch 1, soll CLR Priorität vor LOAD und LOAD Priorität vor SHIFT haben. Im Fall, daß alle 3 Steuersignale CLR, LOAD und SHIFT logisch 0 sind, soll der alte Zustand des Schieberegisters im nächsten Takt beibehalten werden. Bei einem Reset sollen alle 4 Stellen des Schieberegister asynchron zum Taktsignal auf logisch 0 gesetzt werden. Ein Reset soll dabei Priorität gegenüber allen synchronen Aktionen haben. Der Ausgang SREGOUT entspricht einfach der höchstwertigsten Stelle des Schieberegisters. Erklären Sie den Aufbau der Architecture und der dabei verwendeten Statements.

- g) Welche Teile im VHDL-Sourcecode sind für synchrone Schaltungen charakteristisch bzw. haben immer das gleiche Aussehen?

## 4.3. Beschreibung von Addierern, Subtrahierern und Zählern in VHDL

Im Rahmen dieses Beispiels sollen verschiedene Typen von Addierern, Subtrahierern und synchronen Zählern in VHDL implementiert werden. Auf die Angabe des Headers kann in diesem Beispiel ausnahmsweise verzichtet werden.

- a) Geben Sie die Architecture für einen 4-Bit-Addierer an, der die beiden 4-Bit-Operanden OP1 und OP2 addiert und das Ergebnis am 4-Bit-Ausgang SUM ausgibt. Erklären Sie den Aufbau der Architecture und der dabei verwendeten Statements.

- b) Geben Sie die Architecture für einen 4-Bit-Subtrahierer an, der den 4-Bit-Operand OP2 vom 4-Bit-Operand OP1 subtrahiert und das Ergebnis am 4-Bit-Ausgang DIFF ausgibt. Erklären Sie den Aufbau der Architecture und der dabei verwendeten Statements.

- c) Geben Sie die Architecture für einen 4-Bit-Addierer mit Übertragsein- und Ausgang an, der die beiden 4-Bit-Operanden OP1 und OP2 und den Übertragseingang CIN addiert, am 4-Bit-Ausgang SUM ausgibt und bei einem Übertrag des Ergebnisses den Übertragsausgang COUT setzt. Erklären Sie den Aufbau der Architecture und der dabei verwendeten Statements.

- d) Geben Sie die Architecture für einen 6-Bit-Up-/Down-Counter an. Der Counter besitzt den 6-Bit breiten Eingang CNTIN, den 6-Bit breiten Zählerausgang CNTOUT, die synchronen Steuersignale LOAD, CNT und DIR, das Taktsignal CLK und das asynchrone, low-aktive Resetsignal RESETB. Der 6-Bit-Wert am Eingang CNTIN soll als neuer Zählerstand CNTOUT mit der steigenden Flanke des Taktsignals CLK in den Zähler geladen werden, wenn der Zustand von LOAD zu diesem Zeitpunkt logisch 1 ist. Der Zählerstand des Zählers CNTOUT soll mit der steigenden Flanke des Taktsignals CLK um 1 erhöht (DIR = 1) oder um 1 erniedrigt werden (DIR = 0), wenn der Zustand von COUNT zu diesem Zeitpunkt logisch 1 ist und LOAD dabei logisch 0 ist. Andernfalls soll der alte Zählerstand CNTOUT im nächsten Takt beibehalten werden. Bei einem Reset soll der Ausgang CNTOUT des Zählers asynchron zum Taktsignal auf logisch 0 gesetzt werden. Ein Reset soll dabei Priorität gegenüber allen synchronen Aktionen haben. Erklären Sie den Aufbau der Architecture und der dabei verwendeten Statements.

- e) Geben Sie die Architecture für einen 8-Bit-Aufwärtszähler an. Der Counter besitzt die synchronen Steuersignale COUNT, SET0, SET16 und SET64, den 8-Bit breiten Zählerausgang CNTOUT, den Ausgang CNTOUT100, das Taktsignal CLK und das asynchrone, low-aktive Resetsignal RESETB. Der Zählerstand CNTOUT soll mit der fallenden Flanke des Taktsignals CLK auf einen der dezimalen Werte 0, 16 oder 64 gesetzt werden, wenn der Zustand des entsprechenden Steuereingangs SET0, SET16 oder SET64 zu diesem Zeitpunkt logisch 1 ist. Der Zählerstand des Zählers CNTOUT soll hingegen mit der fallenden Flanke des Taktsignals CLK um 1 erhöht werden, wenn der Zustand von COUNT zu diesem Zeitpunkt logisch 1 ist und der Zählerstand kleiner als der dezimale Wert 199 ist. Sind mehrere der Signale SET0, SET16, SET64 und COUNT logisch 1, besitzen die Aktionen die folgende Priorität: SET0, SET16, SET64, COUNT. Der Ausgang CNTOUT100 soll schließlich zumindest für eine Taktperiode lang logisch 1 sein, wenn der Zähler den dezimalen Zählerstand 100 erreicht hat. Bei einem Reset soll der Ausgang CNTOUT des Zählers asynchron zum Taktsignal auf logisch 0 gesetzt werden. Ein Reset soll dabei Priorität gegenüber allen synchronen Aktionen haben. Erklären Sie den Aufbau der Architecture und der dabei verwendeten Statements.

- f) Erklären Sie den Unterschied zwischen VHDL und Low-Level-Gatterbeschreibungssprachen. Welche Aufgaben hat das Synthesetool in VHDL?

g) Vergleichen Sie die Erstellung von Hardware mittels VHDL mit dem Erstellen lauffähiger Programme über eine Hochsprache. Welche Unterschiede bzw. Gemeinsamkeiten lassen sich feststellen? Was kann als eine der wichtigsten Regeln bei der Erstellung von Hardware mittels VHDL angesehen werden?

## 4.4. Beschreibung von Decodern in VHDL

Im Rahmen dieses Beispiels sollen verschiedene Typen von Decodern in VHDL implementiert werden. Auf die Angabe des Headers kann in diesem Beispiel ausnahmsweise verzichtet werden.

- a) Geben Sie die Architecture für den Befehlsdecoder aus Beispiel 3.4 an. Erklären Sie den Aufbau der Architecture und der dabei verwendeten Statements.

- b) Geben Sie die Architecture für das ROM aus Beispiel 3.4 an. Erklären Sie den Aufbau der Architecture und der dabei verwendeten Statements. Was sind Makrozellen?

## 4.5. Beschreibung von Moore- und Mealy-Automaten in VHDL

Im Rahmen dieses Beispiels sollen Moore- und Mealy-Automaten in VHDL implementiert werden. Auf die Angabe des Headers kann in diesem Beispiel ausnahmsweise verzichtet werden.

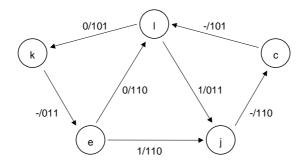

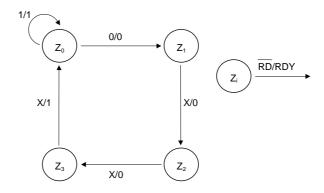

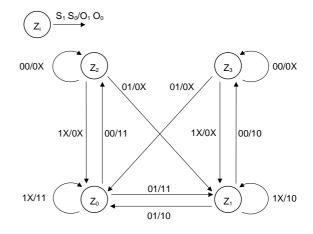

a) Geben Sie die Architecture für den in der folgenden Abbildung gegebenen Moore-Automaten an. Der Automat soll mit positiv flankengetriggerten Flip-Flops realisiert werden. Erklären Sie den Aufbau der Architecture und der dabei verwendeten Statements.

- b) Ändern Sie die Architecture für den unter Punkt a) realisierten Automaten dahingehend, daß der Ausgang X des Automaten frei von Hazards ist.

- c) Geben Sie die Architecture für den in Beispiel 2.4 gegebenen Mealy-Automaten an. Der Automat soll mit positiv flankengetriggerten Flip-Flops realisiert werden und bei einem Reset den Zustand Z0 annehmen. Erklären Sie den Aufbau der Architecture und der dabei verwendeten Statements. Wie erkennt man an Automaten die nach der Struktur von Punkt a) und c) aufgebaut wurden im VHDL-Code auf den ersten Blick, ob es sich um einen Mooreoder einen Mealy-Automaten handelt?

- d) Kann bei einer Beschreibung des in Beispiel 2.4 gegebenen Mealy-Automaten in VHDL, alleine durch die in Beispiel 2.4, Punkt e) gegebene Codierung eine Hazard-Freiheit des Ausgangssignals RDY garantiert werden?

## 4.6. Aufbau von hierarchischen Designs mittels VHDL

Implementieren Sie den Microcontroller aus Beispiel 3.2 in VHDL. Nehmen Sie dazu an, daß die in der Angabe des Beispiels 3.2 gegebenen Blöcke Counter, ROM, Ausgangsregister und Decoder bereits als fertige Entity-/Architecture-Paare existieren und binden Sie diese Komponenten in das Design des Microcontrollers ein (die Entities und Architectures dieser Module müssen nicht angegeben werden). Geben Sie die Architecture des Microcontrollers an. Erklären Sie den Aufbau der Architecture und der dabei verwendeten Statements.

# 5. Simulation, Testen und Design Rules

## 5.1. Design for Testability

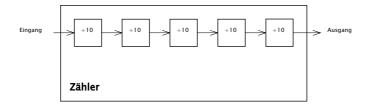

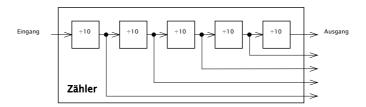

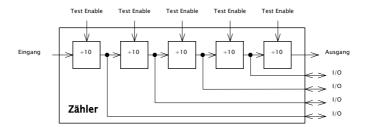

Die Testbarkeit des Schaltwerks aus Beispiel 3.4 soll durch das Hineinführen bzw. Herausführen zusätzlicher Signale in bzw. aus dem Chip erhöht werden. Dazu soll einerseits die Beobachtbarkeit und andererseits die Steuerbarkeit des Systems erhöht werden.

- a) Was versteht man beim ASIC-Design unter den Begriffen Simulation, Testen und Design Rules? Welche Zusammenhänge existieren zwischen den drei Begriffen?

- b) Erfolgen Spezifikation, Beschreibung und Simulation eines ASICs Top Down oder Bottom Up?

- c) Erläutern Sie die Begriffe Beobachtbarkeit und Steuerbarkeit im Bezug auf die Testbarkeit eines Systems an einem einfachen Beispiel.

- d) Erweitern Sie das Schaltbild des Schaltwerks aus Beispiel 3.4 um die Testbarkeit des Designs zu erhöhen. Dazu sollen einerseits die Ausgangssignale des Schaltnetzes SN außerhalb des Chips sichtbar gemacht werden. Des weiteren soll der Program Counter PC im Testmodus mit einer beliebigen Adresse von außen zu laden sein. Am Gehäuse des Chips sind noch 11 unbenutzte Pins vorhanden. Geben Sie das Schaltbild der erweiterten Schaltung an. Wird durch die beiden zusätzlichen Funktionen die Beobachtbarkeit oder die Steuerbarkeit der Schaltung erhöht?

- e) Erläutern Sie die Funktion eines bidirektionalen Pads.

- f) Durch den Einsatz einer neuen Gehäuseform haben Sie nur mehr 2 unbenutzte Pins zur Verfügung um die geforderten Testfunktionen zu realisieren. Geben Sie das Schaltbild der erweiterten Schaltung an, welche die geforderten Testfunktionen realisiert. Sie können dabei annehmen, daß der Zustand der beiden 4-Bit-Ausgangssignale A und B nicht von Interesse ist, solange sich die Schaltung im Testmodus befindet.

### 5.2. Simulation in VHDL

Zur Simulation des D-Flip-Flops aus Beispiel 4.5, Punkt c) ist eine VHDL-Testbench zu schreiben.

- a) Was versteht man unter Logiksimulation und Gate Level Simulation? Was sind die Vor- und Nachteile beider Simulationsmethoden?

- b) Geben Sie eine Testbench zur Simulation des D-Flip-Flops aus Beispiel 4.5, Punkt c) an. Erklären Sie den Aufbau der Testbench und der dabei verwendeten Statements. Auf die Angabe des Headers kann in diesem Beispiel ausnahmsweise verzichtet werden.

- c) Was hätte es für Auswirkungen, wenn das Signal D in die Sensitivity List des in Beispiel 4.5, Punkt c) abgebildeten Prozesses *D\_Flip\_Flop* hinzugefügt werden würde?

- d) Ist die in Punkt b) entwickelte Testbench synthetisierbar? Begründen Sie ihre Antwort.

- e) Mit welchen Problemen hat man als Entwickler zu kämpfen, wenn für Simulationen oder Tests innerer Signale an das Top Level Design des Chips herausgeführt werden müssen?

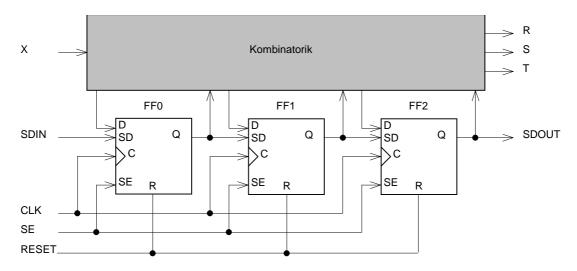

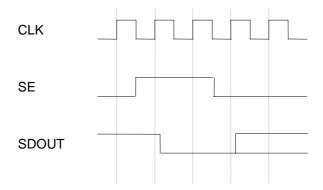

## 5.3. Scan-Path-Design

Der Mealy-Automat aus Beispiel 2.3 soll als Scan-Path Design realisiert werden. Dazu werden alle D-Flip-Flops des Designs durch positiv flankengetriggerte Scan-Flip-Flops ersetzt. Anschließend soll ein Testpattern entworfen werden, welches den Automaten in einen definierten Zustand bringt, von welchem aus das weitere Verhalten des Automaten im Normalbetrieb überprüft werden kann.

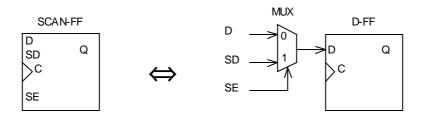

- a) Geben Sie das Schaltbild eines Scan-Flip-Flops mit allen Ein- und Ausgängen an. Durch welche einfache Schaltung kann ein normales D-Flip-Flop in ein Scan-Flip-Flop umgewandelt werden?

- b) Geben Sie das Schaltbild des Mealy-Automaten mit Scan-Flip-Flops an. Die Kombinatorik des Automaten kann dabei als Black Box (Modul mit Ein- und Ausgängen) gezeichnet werden.

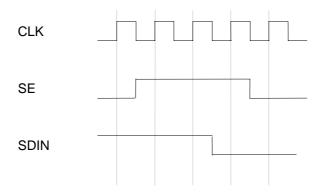

- c) Um wieviele Ein- und Ausgänge erhöht sich die Anzahl der Signale des Automaten bedingt durch das Scan-Path-Design? Wie heißen die neuen Ein- und Ausgänge? Erklären Sie die Funktion der Scan-Path-Kette.

- d) Geben Sie das Timing aller benötigten Signale eines Testpatterns an, um den Automaten in den Zustand e zu versetzen. Anmerkung: Das Testpattern hängt von der gewählten Zustandscodierung des Automaten ab. Beschreiben Sie die Vorgangsweise.

- e) Nachdem der Automat über die Scan-Path-Kette in den Zustand e versetzt wurde, soll nach zwei weiteren aktiven Taktflanken (während denen der Automat sich im Normalbetrieb befindet) der aktuelle Zustand des Automaten über die Scan-Path-Kette ausgelesen werden. Der Eingang x des Automaten ist konstant auf 1 gelegt. Geben Sie das Timing aller benötigten Signale eines Testpatterns an, um den Zustand des Automaten auszulesen. Beschreiben Sie die Vorgangsweise. In welchem Zustand befindet sich der Automat?

- f) Welche Auswirkungen hat ein Vergattern von Takteingängen von Flip-Flops im Bezug auf Scan-Path-Design?

## 1. Moore-Automaten

#### 1.1 Phasenschieber

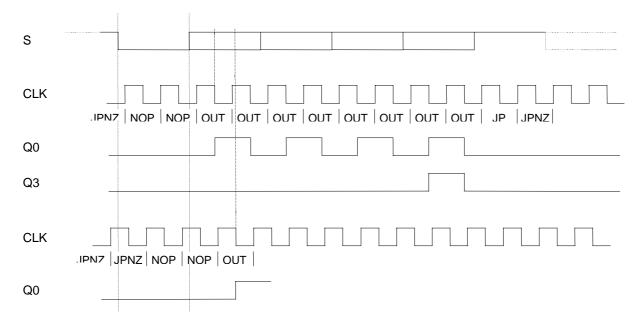

a) Vollständiges Zeitdiagramm:

b) Sinnvolle Wertebereiche von s und daraus folgende Wertebereiche von p:

Minimalwert der Frequenz von s:

$$f_{s,min} = 0 \Rightarrow f_p = f/2$$

(laut Angabe)

Maximalwert der Frequenz von s:

$$f_{s,max} = f/2 \implies f_p = 0$$

(die Halbwelle von p wird ins Unendliche verlängert)

$f_s > f/2$  wäre sinnlos, da Eingangssignale von synchronen Automaten nur ein Mal pro Takt abgefragt werden.

Dazwischen:

z.B.:

$$f_s = f/4 \implies f_p = f/4$$

- c) Haben alle verwendeten Bauteile ein Propagation Delay von 0, bedeutet dies, daß die Ausgänge des Automaten ihre aktuellen Zustände direkt nach der aktiven Taktflanke des Automaten annehmen. Im Timing-Diagramm der Angabe aus Punkt a) ist zu sehen, daß der Ausgang p seinen Zustand sofort nach der steigenden Taktflanke des Taktes f wechselt. Damit muß die steigende Taktflanke die aktive Taktflanke sein und der Automat muß mit positiv flankengetriggerten Flip-Flops realisiert werden.

- d) Bei einem Mealy-Automaten wäre laut Definition das Ausgangssignal p des Automaten direkt vom Eingangssignal s (welches asynchron zu f ist) abhängig. Nach der Angabe erfolgen Zustandswechsel des Signals p aber nur zu Vielfachen der Periodendauer 1/f des Taktes ⇒ Moore-Automat.

- e) Im allgemeinen läßt sich die Anzahl der benötigten Zustände eines Automaten erst nach dem Zeichnen von Zustandsgraph bzw. Zustandsübergangstabelle bestimmen. Bei diesem einfachen Beispiel kann die Anzahl der benötigten Zustände jedoch bereits im vorhinein durch folgende

Überlegung bestimmt werden: Der Zustand des Signals p in der nächsten Halbwelle von p hängt von den Zuständen der beiden Signale p und s in der aktuellen Halbwelle von p ab. Es gibt 4 mögliche Signalkombinationen von p und s, was wiederum 4 Zuständen des Automaten entspricht.

f) Die Ausgangsgleichung für p wird dann möglichst einfach, wenn der Zustand eines Flip-Flops  $Q_i^n$  direkt als Ausgang p verwendet wird. Dies wird durch entsprechende Codierung der Zustände  $Z_i^n \to Q_1^n Q_0^n$  erreicht. Damit degeneriert die Ausgangsgleichung für p zu:

$$p=Q_i^{\ n}$$

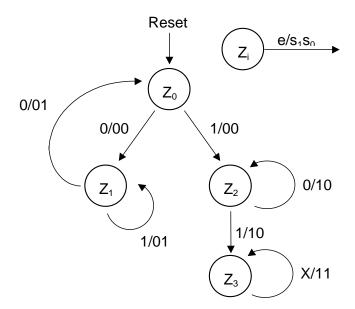

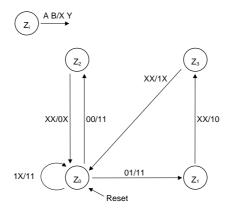

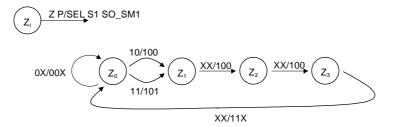

g) Zustandsgraph:

Ändert sich der Zustand des Eingangssignals s nicht, so pendelt der Automat immer zwischen den Zuständen  $Z_0 \leftrightarrow Z_1$  bzw.  $Z_2 \leftrightarrow Z_3$  hin und her und ändert dabei den Zustand des Ausgangs p. Ändert sich hingegen der Zustand von s, so wechselt der Automat zwischen den Zuständen  $Z_0 \leftrightarrow Z_2$  bzw.  $Z_1 \leftrightarrow Z_3$  und p ändert sich bei diesem Übergang nicht.

#### h) Übergangstabelle:

| s <sup>n</sup> | $Q_1^n$ | $Q_0^n$ | $\mathbf{Z}^{n}$ | p <sup>n</sup> | $Q_1^{n+1}$ | $Q_0^{n+1}$ | $Z^{n+1}$      |

|----------------|---------|---------|------------------|----------------|-------------|-------------|----------------|

| 0              | 0       | 0       | $Z_0$            | 0              | 0           | 1           | $Z_1$          |

| 0              | 0       | 1       | $Z_1$            | 1              | 0           | 0           | $Z_0$          |

| 0              | 1       | 0       | $\mathbb{Z}_2$   | 0              | 0           | 0           | $Z_0$          |

| 0              | 1       | 1       | $\mathbb{Z}_3$   | 1              | 0           | 1           | $Z_1$          |

| 1              | 0       | 0       | $Z_0$            | 0              | 1           | 0           | $\mathbb{Z}_2$ |

| 1              | 0       | 1       | $Z_1$            | 1              | 1           | 1           | $\mathbb{Z}_3$ |

| 1              | 1       | 0       | $Z_2$            | 0              | 1           | 1           | $\mathbb{Z}_3$ |

| 1              | 1       | 1       | $\mathbb{Z}_3$   | 1              | 1           | 0           | $\mathbb{Z}_2$ |

Unter Berücksichtigung von Punkt f) wurde  $Q_0^n = p^n$  gewählt. Weiters wurde  $Q_1^n$  so gewählt, daß sich für  $Z_i^n \to Q_1^n Q_0^n$  eine binäre Codierung ergibt (diese Codierung wurde allerdings vollkommen willkürlich so gewählt).

i) Realisierung mit D-Flip-Flops:

Charakteristische Gleichung für D-Flip-Flops:

$$Q^{n+1} = D^n$$

$Q_0^{n+1}$ :

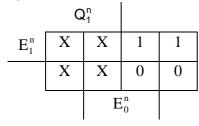

|         | C | ) <sup>n</sup> 0 |   |   |

|---------|---|------------------|---|---|

| $Q_1^n$ | 1 | 0                | 1 | 0 |

|         | 0 | 1                | 0 | 1 |

|         |   | S                | n |   |

Keine Vereinfachung möglich ⇒

$$D_0^n = Q_0^{n+1} = \overline{S^n} Q_1^n Q_0^n \vee \overline{S^n} \overline{Q_1^n} \overline{Q_0^n} \vee S^n Q_1^n \overline{Q_0^n} \vee S^n \overline{Q_1^n} Q_0^n$$

Die Gleichungen für D<sub>1</sub><sup>n</sup> und p können einfach aus der Übergangstabelle abgelesen werden:

$$D_1^n = Q_1^{n+1} = s^n$$

$$p^n = Q_0^n$$

#### 1.2. Schaltknoten

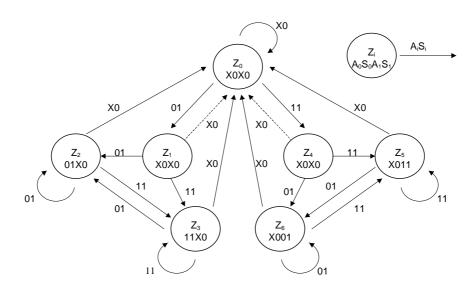

#### a), b) Zustandsgraph:

Die linke Seite des Zustandsgraphen ist für den Ausgangskanal 0, die rechte Seite des Zustandsgraphen ist für den Ausgangskanal 1 zuständig. Um jenen Fehlerfall zu berücksichtigen, daß überhaupt nur ein Adreßbit übertragen wird, ist der Zustandsgraph durch die Übergänge  $Z_1 \rightarrow Z_0$  und  $Z_4 \rightarrow Z_0$  zu ergänzen.

c) Der Automat besitzt 7 Zustände. Mit 3 Flip-Flops können 8 Zustände realisiert werden. Somit werden also 3 Flip-Flops benötigt.

#### d) Zustandsübergangstabelle:

Die Zustände werden hier ganz einfach binär codiert. Wie allerdings schon im Vorlesungsskriptum erläutert ist, kann sich durch die Wahl der Codierung eine Vereinfachung bzw. Verkomplizierung der kombinatorischen Logik des Automaten ergeben. Es kann also im konkreten Fall durchaus sein, daß Sie durch eine andere Codierung einfachere Gleichungen für  $A_0$ ,  $S_0$  und  $D_1$  erhalten.

#### Übergangstabelle:

| $A_{i}$ | $S_{i}$ | $Z^n$          | $Q_2^n$ | $Q_1^n$ | $Q_0^{n}$ | $\mathbb{Z}^{n+1}$ | $Q_2^{n+1}$ | $Q_1^{n+1}$ | $Q_0^{n+1}$ | $A_0$ | $S_0$ | $A_1$        | $S_1$ |

|---------|---------|----------------|---------|---------|-----------|--------------------|-------------|-------------|-------------|-------|-------|--------------|-------|

| X       | 0       | $Z_0$          | 0       | 0       | 0         | $Z_0$              | 0           | 0           | 0           | X     | 0     | X            | 0     |

| X       | 0       | $\mathbf{Z}_1$ | 0       | 0       | 1         | $Z_0$              | 0           | 0           | 0           | X     | 0     | X            | 0     |

| X       | 0       | $\mathbf{Z}_2$ | 0       | 1       | 0         | $Z_0$              | 0           | 0           | 0           | 0     | 1     | $\mathbf{X}$ | 0     |

| X       | 0       | $\mathbb{Z}_3$ | 0       | 1       | 1         | $Z_0$              | 0           | 0           | 0           | 1     | 1     | X            | 0     |

| X       | 0       | $\mathbb{Z}_4$ | 1       | 0       | 0         | $Z_0$              | 0           | 0           | 0           | X     | 0     | X            | 0     |

| X       | 0       | $\mathbb{Z}_5$ | 1       | 0       | 1         | $Z_0$              | 0           | 0           | 0           | X     | 0     | 1            | 1     |

| X       | 0       | $Z_6$          | 1       | 1       | 0         | $Z_0$              | 0           | 0           | 0           | X     | 0     | 0            | 1     |

| X       | 0       | $\mathbb{Z}_7$ | 1       | 1       | 1         | $Z_0$              | 0           | 0           | 0           | X     | 0     | X            | 0     |

| 0       | 1       | $Z_0$          | 0       | 0       | 0         | $Z_1$              | 0           | 0           | 1           | X     | 0     | X            | 0     |

| 0       | 1       | $\mathbf{Z}_1$ | 0       | 0       | 1         | $\mathbb{Z}_2$     | 0           | 1           | 0           | X     | 0     | X            | 0     |

| 0       | 1       | $\mathbf{Z}_2$ | 0       | 1       | 0         | $\mathbb{Z}_2$     | 0           | 1           | 0           | 0     | 1     | X            | 0     |

| 0       | 1       | $\mathbb{Z}_3$ | 0       | 1       | 1         | $\mathbb{Z}_2$     | 0           | 1           | 0           | 1     | 1     | X            | 0     |

| 0       | 1       | $\mathbb{Z}_4$ | 1       | 0       | 0         | $Z_6$              | 1           | 1           | 0           | X     | 0     | X            | 0     |

| 0       | 1       | $\mathbb{Z}_5$ | 1       | 0       | 1         | $Z_6$              | 1           | 1           | 0           | X     | 0     | 1            | 1     |

| 0       | 1       | $Z_6$          | 1       | 1       | 0         | $Z_6$              | 1           | 1           | 0           | X     | 0     | 0            | 1     |

| 0       | 1       | $\mathbb{Z}_7$ | 1       | 1       | 1         | $Z_0$              | 0           | 0           | 0           | X     | 0     | X            | 0     |

| 1       | 1       | $Z_0$          | 0       | 0       | 0         | $\mathbb{Z}_4$     | 1           | 0           | 0           | X     | 0     | X            | 0     |

| 1       | 1       | $\mathbf{Z}_1$ | 0       | 0       | 1         | $\mathbb{Z}_3$     | 0           | 1           | 1           | X     | 0     | X            | 0     |

| 1       | 1       | $\mathbf{Z}_2$ | 0       | 1       | 0         | $\mathbb{Z}_3$     | 0           | 1           | 1           | 0     | 1     | X            | 0     |

| 1       | 1       | $\mathbb{Z}_3$ | 0       | 1       | 1         | $\mathbb{Z}_3$     | 0           | 1           | 1           | 1     | 1     | X            | 0     |

| 1       | 1       | $\mathbb{Z}_4$ | 1       | 0       | 0         | $Z_5$              | 1           | 0           | 1           | X     | 0     | X            | 0     |

| 1       | 1       | $\mathbb{Z}_5$ | 1       | 0       | 1         | $Z_5$              | 1           | 0           | 1           | X     | 0     | 1            | 1     |

| 1       | 1       | $Z_6$          | 1       | 1       | 0         | $Z_5$              | 1           | 0           | 1           | X     | 0     | 0            | 1     |

| 1       | 1       | $\mathbb{Z}_7$ | 1       | 1       | 1         | $Z_0$              | 0           | 0           | 0           | X     | 0     | X            | 0     |

Da mit 3 Flip-Flops 8 Zustände kodiert werden können, der Automat aber nur 7 Zustände hat, wird ein Zustand nicht benötigt. Im Normalfall befindet sich der Automat niemals im Zustand Z7. Durch Verletzung von Setup- bzw. Hold-Zeiten der Flip-Flops des Automaten, kann es in der Realität jedoch prinzipiell durchaus vorkommen, daß der Automat in den Zustand Z7 verzweigt. Für die Wahl des Folgezustands sowie der Ausgangssignale in nicht verwendeten Zuständen gibt es nun mehrere Möglichkeiten:

1) Aufgrund des eher theoretischen Charakters der Aufgabenstellung wird davon ausgegangen, daß der Automat niemals in einen nicht verwendeten Zustand verzweigt. Damit ist der Folgezustand und der Zustand der Ausgangssignale beliebig und für die Folgezustände Qi<sup>n+1</sup> sowie für die Ausgangssignale ai<sup>n</sup> kann in der Übergangstabelle ein X geschrieben werden. Die zur Erzeugung der Ausgangssignale und der Folgezustände benötigte kombinatorische Logik kann sich dadurch dementsprechend vereinfachen. Dies bedingt wiederum, daß man zur Lösung der Übungsbeispiele weit weniger Zeit als vorhergesehen benötigt, man zum Telephonhörer greifen kann um seine(n) Freundin bzw. Freund anzutelephonieren und mit

den Worten "Ich bin fertig mit dem Mist. Kino geht sich also heute doch noch aus …" zum gemütlichen Teil des Abends übergehen kann.

- 2) Der Automat bleibt, so er sich in einem nicht verwendeten Zustand befindet, in demselbigen. In diesem Zustand wird eine spezielle Kombination der Ausgangssignale generiert, wodurch dem Benutzer das Auftreten eines nicht erwünschten Zustandes signalisiert wird. Durch einen vom Benutzer initiierten Reset des Automaten kann dieser (der Automat, nicht der Benutzer) anschließend wieder in einen "normalen" Zustand gebracht werden.

- 3) Als Folgezustand wird ein "sinnvoller" Zustand des Automaten gewählt. Ein "sinnvoller" Zustand kann etwa der Zustand nach einem Reset des Automaten oder der Ruhezustand des Automaten sein. Was genau ein "sinnvoller" Zustand ist, hängt jeweils von der Aufgabenstellung ab und kann nicht allgemein beantwortet werden. Auf jeden Fall muß darauf geachtet werden, daß in einem nicht verwendeten Zustand des Automaten die Ausgangssignale keine "gefährlichen" Zustände annehmen. Was ein "gefährlicher" Zustand ist, hängt wiederum von der Aufgabenstellung ab.

Ich empfehle sowohl in der Praxis, als auch für die Übungen, solange von der Angabe nichts anderes gefordert wird, Variante 3 (Sorry, nix is mit Kino ...). Als Folgezustand für Zustand  $Z_7$  wird hier also Zustand  $Z_0$  gewählt, was der Ruhezustand des Automaten ist. Wichtig ist außerdem, daß der Zustand der Ausgangssignale  $S_0$  und  $S_1$  im Zustand  $Z_7$  low ist.

e) Bestimmung der Gleichungen für A<sub>0</sub>, S<sub>0</sub> und D<sub>1</sub>:

Wie aus der obigen Übergangstabelle zu sehen ist, sind  $A_0$  und  $S_0$  von  $A_i$  und  $S_i$  unabhängig, wodurch sich die KV-Diagramme für  $A_0$  und  $S_0$  auf drei Variable beschränken.

$$A_0 = Q_0^n$$

Nachdem in der Angabe nichts über den Zustand von  $A_0$  ausgesagt wird während  $S_0$  low ist, kann durch entsprechende Wahl der "don`t care"-Felder im KV-Diagramm die Gleichung für  $A_0$  erheblich vereinfacht werden.

$S_0^n$ :

$$S_0 = \overline{Q_2}^n Q_1^n$$

Charakteristische Gleichung für D-Flip-Flops:

$$O^{n+1} = D^n$$

$$Q_1^{n+1}$$

(für  $S_i = 1$ ):

|   | `          | C | )n 1 |            |   |                             |

|---|------------|---|------|------------|---|-----------------------------|

|   | <b>o</b> n | 1 | 1    | 1          | 1 |                             |

|   | $Q_0^n$    | 0 | 0    | 0          | 1 | C <sup>n</sup>              |

| _ |            | 1 | 0    | 0          | 1 | Q <sub>2</sub> <sup>n</sup> |

|   |            | 1 | 1    | 0          | 0 |                             |

|   | A          |   |      | <b>\</b> i |   | •                           |

$$D_1^n = Q_1^{n+1} = S_i \wedge (Q_1^n \cdot \overline{Q_2^n} \vee Q_0^n \cdot \overline{Q_2^n} \vee \overline{Q_1^n} \vee \overline{Q_1^n} \cdot \overline{Q_2^n} \cdot \overline{A_i} \vee \overline{Q_0^n} \cdot Q_1^n \cdot \overline{A_i})$$

f) Für eine Vermittlungsanlage mit einem Sender und 6 Empfängern werden 6 Schaltknoten benötigt. Durch die Hintereinanderschaltung von 3 Schaltknoten werden pro Paket 3 Adreßbits benötigt. Zusammen mit den 8 Datenbits ergibt sich eine Paketlänge von 11 Bits.

## 1.3. Gray-Code Zähler

a) Charakteristische Gleichung des JK-FF:

$$Q^{n+1} = J^n \cdot \overline{Q^n} \vee \overline{K^n} \cdot Q^n$$

b) Übergangstabellen des JK-FF:

| J | K | $Q^{n+1}$        |

|---|---|------------------|

| 0 | 0 | Q <sup>n</sup>   |

| 0 | 1 | 0                |

| 1 | 0 | 1                |

| 1 | 1 | $\overline{Q^n}$ |

| Q <sup>n</sup> | $Q^{n+1}$ | J | K |

|----------------|-----------|---|---|

| 0              | 0         | 0 | X |

| 0              | 1         | 1 | X |

| 1              | 0         | X | 1 |

| 1              | 1         | X | 0 |

|                |           |   |   |

c), d) KV-Diagramm für  $Q_3^{n+1}$ ,  $Q_2^{n+1}$ ,  $Q_1^{n+1}$  und  $Q_0^{n+1}$ :

|                       |   |   |   |   |   |   |   | Ç | $\mathbf{Q}_0$ |   |   |   |   |   |   |   |                |

|-----------------------|---|---|---|---|---|---|---|---|----------------|---|---|---|---|---|---|---|----------------|

|                       | 1 | 1 | 1 | 0 | 1 | 1 | 0 | 0 | 1              | 1 | 0 | 1 | 1 | 0 | 0 | 1 |                |

| $Q_3$                 | 1 | 1 | 0 | 0 | 1 | 1 | 0 | 1 | 1              | 0 | 0 | 1 | 1 | 0 | 0 | 0 |                |

| <b>Q</b> <sub>3</sub> | 0 | 1 | 1 | 0 | 1 | 0 | 1 | 1 | 0              | 0 | 1 | 1 | 1 | 0 | 0 | 0 |                |

|                       | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 1              | 0 | 1 | 1 | 1 | 0 | 1 | 0 | 0              |

|                       | 0 | 1 | 0 | 0 | 1 | 1 | 1 | 1 | 0              | 0 | 0 | 1 | 1 | 0 | 1 | 0 | $\mathbf{Q}_1$ |

|                       | 0 | 1 | 1 | 0 | 0 | 1 | 1 | 1 | 0              | 0 | 1 | 1 | 0 | 0 | 1 | 0 |                |

|                       | 0 | 1 | 0 | 1 | 0 | 1 | 1 | 1 | 0              | 0 | 0 | 0 | 0 | 0 | 1 | 0 |                |

|                       | 0 | 1 | 0 | 0 | 0 | 1 | 0 | 1 | 0              | 0 | 0 | 1 | 0 | 0 | 0 | 0 |                |

| $Q_2$                 |   |   |   |   |   |   |   |   |                |   |   |   |   |   |   |   |                |

e) KV-Diagramme für  ${J_3}^n,\, {J_2}^n,\, {J_1}^n,\, {J_0}^n$  und  ${K_3}^n,\, {K_2}^n,\, {K_1}^n,\, {K_0}^n$ :

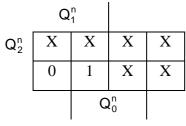

| $J_3^n$ : |       |   | Ç  | $\mathbf{Q}_0$ |   |       |

|-----------|-------|---|----|----------------|---|-------|

|           | 0     | X | X  | X              | X |       |

|           | $Q_3$ | X | X  | X              | X |       |

| •         |       | 0 | 1  | 0              | 1 | $Q_1$ |

|           |       | 0 | 0  | 0              | 0 |       |

|           |       | C | )2 |                |   |       |

| $K_3^n$ : |       |   | Ç                     | $\mathbf{Q}_0$ |   |       |

|-----------|-------|---|-----------------------|----------------|---|-------|

|           | $Q_3$ | 0 | 0                     | 0              | 0 | •     |

|           |       | 1 | 0                     | 1              | 0 | 0     |

| •         |       | X | X                     | X              | X | $Q_1$ |

|           |       | X | X                     | X              | X |       |

|           |       | Ç | <b>)</b> <sub>2</sub> |                |   |       |

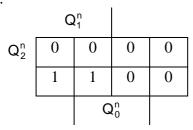

| $J_2^n$ : |       |   | Ç                     | 0 |   |                |

|-----------|-------|---|-----------------------|---|---|----------------|

|           | 0     | X | X                     | 1 | 0 |                |

|           | $Q_3$ | X | X                     | 0 | 0 |                |

| -         |       | X | X                     | 0 | 0 | $\mathbf{Q}_1$ |

|           |       | X | X                     | 0 | 0 |                |

|           |       | Ç | <b>)</b> <sub>2</sub> |   |   | 1              |

| $\mathbf{K}_{2}^{n}$ : |       |   | Ç                     | $\mathbf{Q}_0$ |   |       |

|------------------------|-------|---|-----------------------|----------------|---|-------|

|                        | 0     | 0 | 0                     | X              | X | •     |

|                        | $Q_3$ | 0 | 1                     | X              | X |       |